# LonWorks® Microprocessor Interface Program(MIP) User's Guide

**Revision 3**

078-0017-01C

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Echelon Corporation.

ţ

Echelon, LON, Neuron, LonBuilder, LonManager, LonTalk, LONWORKS, 3120, and 3150 are registered trademarks of Echelon Corporation. Other names may be trademarks of their respective companies.

Document No. 29500

Printed in the United States of America. Copyright ©1992, 1993, 1995 by Echelon Corporation

Echelon Corporation 4015 Miranda Avenue Palo Alto, California 94304

# Preface

This document describes how to build a LONWORKS<sup>\*</sup> network interface using the LONWORKS Microprocessor Interface Program (MIP). The MIP is firmware for the Neuron Chip that transforms the Neuron Chip into a communications coprocessor for an attached host processor. The MIP moves the upper layers of the LonTalk<sup>\*</sup> Protocol from the Neuron Chip to the attached host. Network interfaces based on the MIP can be used to create host applications on a variety of host processors including PCs, work-stations, microprocessors, and microcontrollers.

Three MIPs are described in this document. The first two, the MIP/P20 and MIP/P50, use an 11-bit parallel interface to the host processor. The third, the MIP/DPS, uses a dual-ported RAM with hardware semaphores for communicating with the host processor. The MIP/P20 and MIP/P50 are included with the Model 23200 LONWORKS MIP/P20 and MIP/P50 Developer's Kit. The MIP/DPS is included with the Model 23210 LONWORKS MIP/DPS Developer's Kit.

## Audience

The LONWORKS MIP User's Guide is intended for LONWORKS developers who are developing one of the following:

- a LONWORKS network interface that will be embedded within an application node that includes a host processor; the network interface provides an interface between the host processor and a LONWORKS network

- a generic LONWORKS network interface that will be provided for use by third parties who will integrate the network interface with a host processor to create an application node

Programming examples are shown in ANSI C, however, network drivers and host applications may be written in any language that can implement the LONWORKS network interface protocol. Readers of this guide developing network drivers or host applications should have C programming experience and be familiar with LONWORKS concepts and LONWORKS application node development. See *Related Manuals* later in the preface for a list of LONWORKS documentation.

A LonBuilder Developer's Workbench, or a LONWORKS NodeBuilder Development Tool is required to develop a network interface based on any version of the MIP. Once a network interface is developed, these tools are not required to create a host application.

## Content

The LONWORKS MIP User's Guide has six chapters as follows:

- Chapter 1, MIP Overview, provides an introduction to the MIP.

- Chapter 2, *Installing the MIP Software*, describes how to install the MIP software on a PC.

- Chapter 3, *Creating a MIP Image*, describes the process of building the MIP image that will be loaded onto a network interface.

- Chapter 4, *Building a Network Interface*, describes the process of building a network interface with the MIP.

- Chapter 5, *Creating a Network Driver*, describes the process of building a network driver for a host that is to be connected to a MIP-based network interface.

- Chapter 6, *Installing the DOS Network Driver*, describes how a MIP network driver is installed on a DOS host.

# **Related Manuals**

The following manuals and engineering bulletins provide supplemental information to the material in this guide:

• The LONWORKS Host Application Programmer's Guide (document no. 29400) describes how to create LONWORKS host applications. Host applications are application programs running on hosts other than Neuron Chips that use the LonTalk Protocol to communicate with nodes on a LONWORKS network. Network interfaces based on the MIP provide the communications interface between a host application and a LONWORKS network.

- The Parallel I/O Interface to the Neuron Chip engineering bulletin describes the hardware interface used by the MIP/P20 and MIP/P50.

- The LonBuilder User's Guide lists and describes all tasks related to LONWORKS application development using the LonBuilder Developer's Workbench. Refer to that guide for detailed information on the user interface to the LonBuilder software.

- The NodeBuilder User's Guide lists and describes all tasks related to LONWORKS application development using the NodeBuilder Development Tool. Refer to that guide for detailed information on the user interface to the NodeBuilder software.

- The Neuron C Programmer's Guide outlines a recommended general approach to developing Neuron C applications, and explains key concepts of programming in Neuron C through the use of code fragments and examples.

- The Neuron C Reference Guide provides a complete reference section for Neuron C.

- The Custom Node Development engineering bulletin describes the steps for building an example LONWORKS application node.

- The LonTalk Protocol engineering bulletin describes the LonTalk Protocol.

- The Neuron Chip Data Book, Appendix B, provides a description of the network management and diagnostic message formats that must be handled by host application nodes.

- The LONWORKS Network Services Architecture Technical Overview describes how to create host applications that install, maintain, monitor, or control LONWORKS networks.

- The LONWORKS Component Architecture document describes how to create host applications for Microsoft Windows '95 and Windows NT.

- The LonManager DDE Server User's Guide describes how to create network monitoring and control applications based on the LonManager DDE Server. The LonManager DDE Server greatly simplifies user interface and database application development on Microsoft Windows-based hosts.

# Contents

| Preface                                 | i    |

|-----------------------------------------|------|

| Audience                                | ii   |

| Content                                 | ii   |

| Related Materials                       | ii   |

| Chapter 1 MIP Overview                  | 1-1  |

| LONWORKS Network Interface Architecture | 1-2  |

| LONWORKS MIP Developer's Kit            | 1-6  |

| New Features                            | 1-6  |

| Chapter 2 Installing the MIP Software   | 2-1  |

| Software Installation Instructions      | 2-2  |

| Software Contents                       | 2-3  |

| Upgrading from Previous Releases        | 2-6  |

| Chapter 3 Creating a MIP Image          | 3-1  |

| Writing the MIP Application             | 3-2  |

| Example MIP Application for the MIP/P20 | 3-2  |

| Example MIP Application for the MIP/P50 | 3-3  |

| Example MIP Application for the MIP/DPS | 3-4  |

| Specifying MIP Pragmas                  | 3-5  |

| Declaring MIP I/O Objects               | 3-8  |

| Calling the MIP Function                | 3-8  |

| Building the MIP Image                  | 3-10 |

| Loading the MIP Image                   | 3-11 |

| Chapter 4 Building a Network Interface  | 4-1  |

| Building a Network Interface Hardware   | 4-2  |

| Building the Host Interface             | 4-2  |

| MIP/P20 and MIP/P50 Host Interface      | 4-3  |

| MIP/DPS Host Interface                  | 4-5  |

| Handling Uplink Requests                | 4-5  |

| Polled I/O                              | 4-6  |

| Interrupt-Driven I/O                    | 4-6  |

| Implementing a Reset Latch              | 4-9  |

| Implementing Semaphores                 | 4-10 |

|                                         |      |

| Chapter 5 Creating a Network Driver              | 5-1  |

|--------------------------------------------------|------|

| Implementing a Network Driver                    | 5-2  |

| Example Network Driver                           | 5-5  |

| Implementing a MIP/P20 or MIP/P50 Network Driver | 5-5  |

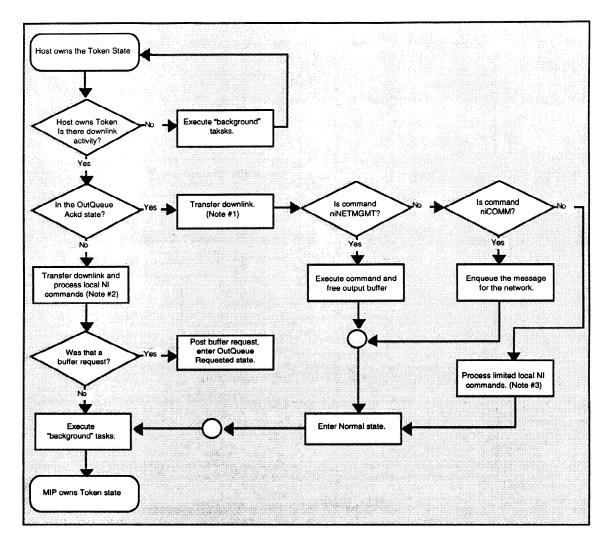

| Downlink Buffer Transfer                         | 5-6  |

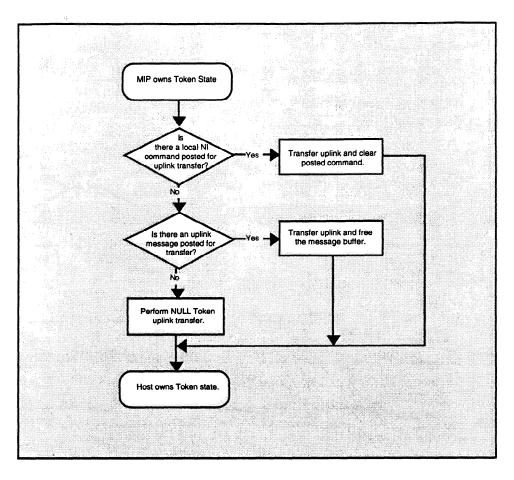

| Uplink Buffer Transfer                           | 5-8  |

| Example MIP/P20 and MIP/P50 Network Driver       | 5-9  |

| MIP/P20 and MIP/P50 Processing                   | 5-10 |

| Implementing a MIP/DPS Network Driver            | 5-13 |

| Control Interface Structure                      | 5-14 |

| <b>Resource Control and Semaphores</b>           | 5-14 |

| Downlink Buffer Transfer                         | 5-15 |

| Uplink Buffer Transfer                           | 5-16 |

| Local Command Processing                         | 5-16 |

| Example MIP/DPS Network Driver                   | 5-17 |

| Chapter 6 Installing the DOS Network Driver      | 6-1  |

| Installing the Sample Network Driver             | 6-2  |

|                                                  |      |

| Appendix A MIP/DPS Control Structures            | A-1  |

| MipPtr                                           | A-2  |

| mipci_outbuffs_s                                 | A-2  |

| mipci_inbuffs_s                                  | A-2  |

| control_iface_s                                  | A-3  |

| Appendix B Example MIP/DPS Control Schematic     | B-1  |

| Memory Map                                       | B-2  |

| Example Notes                                    | B-2  |

# 1

# **MIP Overview**

Welcome to Release 1.1 of the LONWORKS MIP/DPS Developer's Kit and Release 2.3 of the LONWORKS MIP/P20 and MIP/P50 Developer's Kit. These kits enable you to create LONWORKS network interfaces. These network interfaces can be used to create host applications that communicate using the LonTalk protocol and run on processors other than the Neuron Chip.

Host applications and network interfaces extend the reach of LONWORKS technology to a variety of hosts including PCs, workstations, embedded microprocessors, and microcontrollers.

This manual describes how to build a network interface using one of the MIPs. See the LONWORKS Host Application Programmer's Guide for a description of how to write a host application.

A host application combined with a LONWORKS network interface may be used to:

- Add processing power to a LONWORKS network

- Move an existing product to a LONWORKS network

- Implement a network management, monitoring, or control tool based on the LonManager API

This chapter provides an overview of the MIP products. The architecture of a network interface based on the MIP is described, and the components of the MIP Developer's Kits are described. New features also are described.

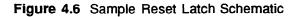

## LONWORKS Network Interface Architecture

A network interface is a device that provides a communications interface between a host processor and a LONWORKS network. The network interface may be a turnkey device such as the SLTA/2 Serial LonTalk Adapter, the PCLTA PC LonTalk Adapter, or the PCNSS PC Interface Card. A custom network interface may be based on the LTM-10 LonTalk Module, LTS-10 Serial LonTalk Adapter module, the LonManager NSS-10 Network Services Server module, or may contain a Neuron Chip running the Microprocessor Interface Program (MIP), and support circuitry. Network interfaces also include a LONWORKS transceiver to connect the Neuron Chip to the communications medium.

The MIP is firmware that transforms the Neuron Chip into a communications coprocessor for an attached host processor. The MIP moves the upper layers of the LonTalk Protocol from the Neuron Chip to the attached host. Three MIPs are available which support different interfaces to the host. The three MIPs are:

- MIP/P20. Uses an 11-bit parallel interface between the host and network interface Neuron Chip. The host can view the Neuron Chip as an 8-bit I/O port with 3 handshake and control lines, or as two 8-bit memory-mapped locations. The MIP/P20 can be run on a Neuron 3120 Chip or a Neuron 3150 Chip, but is usually used only with the Neuron 3120 Chip.

- MIP/P50. Uses an 11-bit parallel interface between the host and network interface Neuron Chip, with the addition of an optional uplink interrupt generated by a memory write from the Neuron Chip. As with the MIP/P20, the host can view the Neuron Chip as an 8-bit I/O port with 3 handshake and control lines, or as two 8-bit memory-mapped locations. The MIP/P50 provides faster throughput than the MIP/P20, even if the uplink interrupt is not used, but it requires a Neuron 3150, 3120E1, or 3120E2 Chip. Use of the uplink interrupt requires a Neuron 3150 Chip. The MIP/P50 firmware and interrupt decoding hardware is included on the LTM-10 LonTalk Module.

- **MIP/DPS.** Uses a dual-ported memory interface between the host and network interface Neuron Chip. The dual ported memory must provide hardware semaphores to control access to the shared memory by either the host or network interface. The MIP/DPS provides faster throughput and lower host overhead than either the MIP/P20 or the MIP/P50, but requires a Neuron 3150 Chip and a high-speed dual ported memory chip compatible with the IDT71342 or Cypress 78144. The MIP/DPS is typically used with high-end 32-bit microprocessors, but it may be used with any host processor.

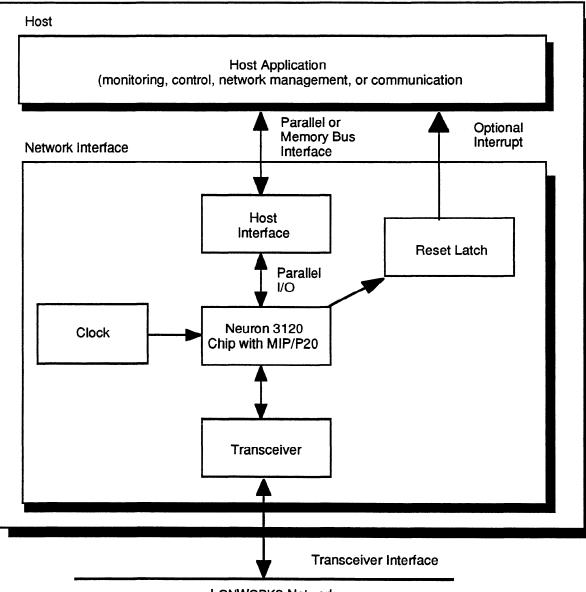

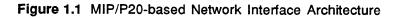

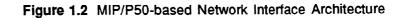

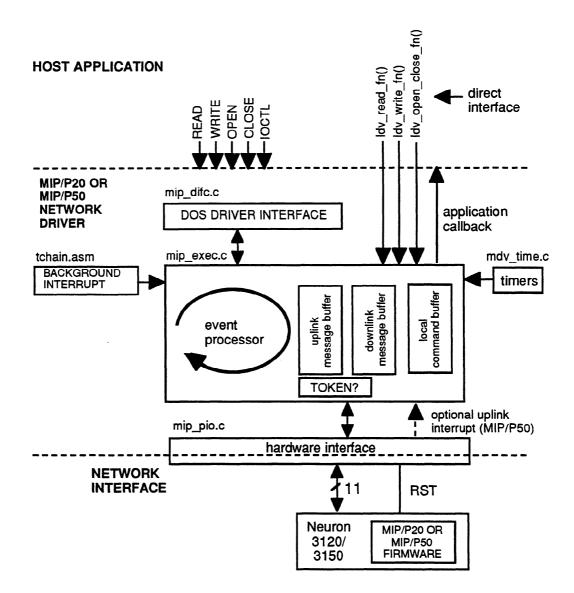

Figure 1.1 illustrates the architecture of a network interface based on the MIP/P20. Figure 1.2 illustrates the architecture of a network interface based on the MIP/P50. Figure 1.3 illustrates the architecture for a MIP/DPS-based network interface. Host-based Node with MIP/P20

LONWORKS Network

Host-based Node with MIP/P50

Host-based Node with MIP/P50

LONWORKS Network

### LONWORKS MIP Developer's Kits

Two developer's kits are available for the MIP. The LONWORKS MIP/P20 and MIP/P50 Developer's Kit includes the software required to build a custom network interface based on the MIP/P20 and MIP/P50. The LONWORKS MIP/DPS Developer's Kit provides similar components for the MIP/DPS. The kits include:

- Microprocessor Interface Program (MIP). The MIP is firmware for the Neuron Chip that extends the Neuron Chip firmware. The MIP is delivered as an object library that is linked with a Neuron C MIP application program to create the MIP image.

- Sample MIP Application. The MIP application is a short Neuron C program that specifies the configuration of the MIP node and invokes the MIP function.

- Sample Network Driver. An example DOS device driver for the MIP. The network driver provides a device independent interface to the host application. This allows host applications to work transparently with different network interfaces, regardless of their physical interface. For example, a host application can be moved from a PCLTA PC LonTalk Adapter to an Echelon SLTA/2 Serial LonTalk Adapter to a custom network interface based on any of the MIPs without being modified. The sample driver is provided as ANSI C and assembly source code that can be modified for different host interfaces to the network interface.

- **Example Host Application**. A sample host application that polls, writes, and monitors network variables, and responds appropriately to network management messages. The example is provided as ANSI C source code that can be used as a starting point for creating custom host applications.

This documentation describes Release 2.3 of the LONWORKS MIP/P20 and MIP/P50 Developer's Kit, and Release 1.1 of the LONWORKS MIP/DPS Developer's Kit.

#### **New Features**

Release 2.3 of the MIP/P20 and MIP/P50 and Release 1.1 of the MIP/DPS include the following new features:

- **Custom Uplink Interrupt Interface.** The MIP/P50 now supports a custom uplink interrupt request function to support custom interrupt request hardware.

- Easier to use host application. The host application example has been enhanced. The network interface (NI) layer now uses a call-back architecture to invoke user-supplied routines to handle all types of incoming messages. This architecture is compatible with the architecture of the host application example provided with the LonManager NSS for Windows and the LonManager NSS-10 Network Services Server Developer's Kits. The host application also transparently handles retries of incoming request messages.

# Installing the MIP Software

This chapter explains how to install the MIP software on a PC, and describes the software files installed during the installation process. Upgrades from previous releases are also described.

# Software Installation Instructions

Follow these steps to install the MIP software on your PC. LonBuilder 3.0 or NodeBuilder 1.5 (or later) is required.

- Place the installation disk in a floppy disk drive. Drive A: is used in the following steps; substitute your drive letter if you are using a drive other than A:. The installation disk is labeled LONWORKS MIP/P20 and MIP/P50 Software for the MIP/P20 and MIP/P50; the installation disk is labeled LONWORKS MIP/DPS Software for the MIP/DPS.

- **2** Start the automatic installation procedure by entering:

a:install →

Enter the drive letter of your floppy drive in place of the "a:" if you are using another drive.

**3** After a moment of disk activity, the product name and version number will be displayed, along with the following message:

Press [Esc] to quit, any other key to continue . . .

The installation can be aborted at any time by pressing the [Esc] key. To continue with the installation, press any other key.

- 4 The next screen provides some basic instructions concerning installation. Press any key (other than [Esc]) to continue.

- 5 The next screen allowsyou to select whether you are installing the software into a LonBuilder software installation, or into a NodeBuilder software installation. Press → when the proper choice is highlighted.

- 6 A list of available hard disk drives will be displayed. Use the arrow keys to select the drive. Press  $\rightarrow$  when the proper drive is highlighted.

- 7 A prompt for an installation directory will be displayed. Enter the name of a directory. The default directory is \LB or \LONWORKS. Press → when the proper path is shown.

- 8 A number of compressed files will now be copied from the floppy to your hard disk, where they will be expanded. When all the files have been placed on your hard disk, you will be returned to DOS.

- **9** A network driver as described in Chapters 5 and 6 must loaded on your host processor before you can run a host application. If your host processor is a PC running DOS, the network driver must be specified in your config.sys file before you can run a host application on the PC. See Chapters 5 and 6 for more information.

# Software Contents

The software for the MIP developer's kits is supplied on installation diskettes which contain the following:

Microprocessor Interface Program (MIP). The MIPs are contained in library files. For NodeBuilder installations, these files are installed in the LONWORKS IMAGES directory (the default directory is \LONWORKS\IMAGES). For LonBuilder installations, these files are installed in the version 3, 4, and 6 IMAGES directory (the default directories are \LB\IMAGES\VER3, \LB\IMAGES\VER4, and \LB\IMAGES\VER6). The filenames for the libraries are:

| File Name   | MIP/Px0 | MIP/DPS | Description                                                                                       |

|-------------|---------|---------|---------------------------------------------------------------------------------------------------|

| mip_pio.lib | •       |         | Parallel I/O MIP library. Includes the MIP/P20 and MIP/P50.                                       |

| mip_dps.lib |         | •       | MIP/DPS library. This library file may only be<br>used with VER4 and VER6 Neuron Chip<br>firmware |

| miput16.1ib | •       | •       | Library functions used by the MIP libraries.                                                      |

Sample MIP Application. The sample MIP applications are contained in Neuron C source files. For NodeBuilder installations, these files are installed in the NB\EXA\MIP directory (the default directory is \LONWORKS\NB\EXA\MIP). For LonBuilder installations, the files are installed in the EXAMPLES\MIP directory (the default directory is \LB\EXAMPLES\MIP). The filenames for the MIP applications are:

| File Name   | MIP/Px0 | MIP/DPS | Description                     |  |

|-------------|---------|---------|---------------------------------|--|

| mip_ap20.nc | •       |         | MIP application for the MIP/P20 |  |

| mip_ap50.nc | •       | Į       | MIP application for the MIP/P50 |  |

| mip_dps.nc  |         | •       | MIP application for the MIP/DPS |  |

Sample Network Driver Source. The example DOS device drivers for the MIP are provided as ANSI C and assembly source files. For NodeBuilder installations, the sample network driver for the MIP/P20 and MIP/P50 is installed in the NB\EXA\MIP directory (the default directory is \LONWORKS\NB\EXA\MIP). For LonBuilder installations, the sample network driver for the MIP/P20 and MIP/P50 is installed in the EXAMPLES\MIP directory (the default directory is \LB\EXAMPLES\MIP).

For NodeBuilder installations, the sample network driver for the MIP/DPS is installed in the NB\EXA\MIP\_DPS directory (the default directory is \LONWORKS\NB\EXA\MIP). For LonBuilder installations, the sample network driver for the MIP/DPS is installed in the EXAMPLES\MIP\_DPS directory (the default directory is \LB\EXAMPLES\MIP\_DPS). The sample network driver ANSI C source files are:

| File Name             | MIP/Px0 | MIP/DPS | Description                                                                                                                                                                                |

|-----------------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dps_frst.c            |         | •       | Device driver header. Must be the first file linked.                                                                                                                                       |

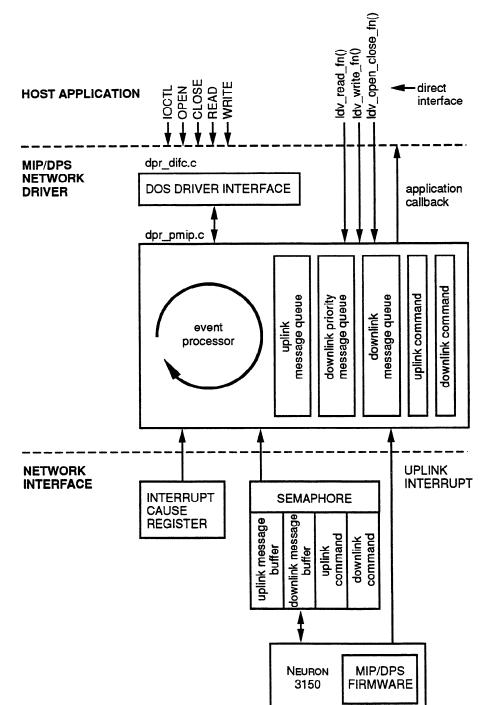

| dps_difc.c            |         | •       | DOS to network driver interface functions.                                                                                                                                                 |

| dps_mip.c             |         | •       | Low-level interface functions for the dual-ported RAM.                                                                                                                                     |

| dps_last.c            |         | •       | Used to determine the size of the network driver.<br>Must be the last file linked.                                                                                                         |

| mip_frst.c            | •       |         | Device driver header. Must be the first file linked.                                                                                                                                       |

| mip_difc.c            | •       |         | DOS to network driver interface functions.                                                                                                                                                 |

| <pre>mip_last.c</pre> | •       |         | Used to determine the size of the device driver.<br>Must be the last file linked.                                                                                                          |

| mip_pio.c             | •       |         | Low-level interface functions to the MIP/P20 or<br>MIP/P50 via the user implemented parallel port.<br>Stub operations are provided that are replaced<br>with code for the actual hardware. |

| mip_exec.c            | •       |         | Medium and high-level interface functions for<br>the driver. Includes the read(), write(), open(),<br>close(), and ioctl() functions.                                                      |

| mdv_time.c            | •       |         | Contains functions which support the usage of<br>the PC/AT's counter # 0 hardware for timeouts<br>required by various parts of the driver.                                                 |

The ANSI C header files are:

| File Name  | MIP/Px0 | MIP/DPS | Description                                                                                                                                  |

|------------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| dpr_defs.h |         | •       | Hardware and buffer definitions for the MIP/DPS.                                                                                             |

| dpr_prto.h |         | •       | Control interface structure definitions and function prototypes for the MIP/DPS.                                                             |

| mip_typs.h | •       |         | Control interface structure definitions and function prototypes type declarations for the MIP/P20 and MIP/P50 network driver C source files. |

| mdv_time.h | •       |         | Structure and constant definitions, and function prototypes for the services associated with the file MDV_TIME.C.                            |

| mip_drvr.h | •       | •       | Network driver structure, command, and return code definitions.                                                                              |

The assembly source files are:

| File Name   | MIP/Px0 | MIP/DPS | Description                                                                  |  |

|-------------|---------|---------|------------------------------------------------------------------------------|--|

| segdata.asm | •       | •       | Segment data constants. This file is the same for both kits.                 |  |

| tchain.asm  | •       |         | Timer interrupt chaining code for the MIP/P20<br>and MIP/P50 network driver. |  |

#### The build files are:

| File Name |   |   | Description                                                                                                                                                                                                                                        |

|-----------|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| makefile  | • | • | Borland C make file. Type make at the DOS command prompt to execute the build instructions in this file.                                                                                                                                           |

| pmip.cfg  | • | • | Borland C compiler options for makefile. The<br>last line of this file contains the Borland C<br>include file path. If the Borland C include file<br>are not contained in the directory<br>C:\BORLANDC\INCLUDE, then this file must be<br>changed. |

The driver has been compiled with Borland C++, version 3.1. Modifications may be required for other compilers such as Microsoft C. Full descriptions of the contents of each of these files are included as comments within the files.

**Example host application**. The example host application is provided as ANSI C source files. These files are installed in the directory EXAMPLES\HA, or \NB\EXA\HA. For a complete description of this example host application, see the LONWORKS Host Application Programmer's Guide.

| File Name  | Description                                                                                                                                                                                                           |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| applmsg.c  | Contains the function definitions for handling network management and network variable messages.                                                                                                                      |  |

| applcmds.c | Contains the code for the user commands to the application.                                                                                                                                                           |  |

| ha.c       | The main line code for this example.                                                                                                                                                                                  |  |

| hauif.c    | Contains the functions for a primitive command-line user interface.                                                                                                                                                   |  |

| ioctl.c    | Contains the functions required to establish<br>communication with a DOS device driver. This file is<br>required only when using the Microsoft C compiler<br>(the Borland C standard library includes this function). |  |

| ldvintfc.c | Contains the lowest-level interface to the DOS network driver.                                                                                                                                                        |  |

| ni_callb.c | Contains functions to handle callbacks from the network driver.                                                                                                                                                       |  |

| ni_msg.c   | Network interface initialization and LonTalk message<br>send and receive functions. Generic functions that<br>can be used by any host application.                                                                    |  |

| applmsg.h  | Contains prototype declarations for the functions defined in applmsg.c.                                                                                                                                               |  |

| ha_comn.h  | Contains common declarations used by all the files in the application.                                                                                                                                                |  |

| hauif.h    | Contains prototype declarations for the functions defined in hauif.c.                                                                                                                                                 |  |

| ldvintfc.h | Contains prototype declarations for the functions defined in ldvintfc.c.                                                                                                                                              |  |

| ni_callb.h | Contains prototype declarations for the functions defined in ni_callb.c.                                                                                                                                              |  |

| ni_msg.h   | Defines network interface message structures.                                                                                                                                                                         |  |

| ni_mgmt.h  | Defines the subset of network management functions used by the sample host application.                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| makefile   | Borland C make file. Type make at the DOS command prompt to execute the build instructions in this file.                                  |

| msoft.mak  | Makefile for Microsoft C compiler. Type make /f<br>msoft.mak at the DOS command prompt to execute<br>the build instructions in this file. |

| ha_v3.xif  | Host-based node external interface file.                                                                                                  |

| ha_test.nc | Neuron C source code for a LONWORKS device that<br>may be bound to a host processor running the<br>sample host application.               |

| display.h  | Display driver functions for the Gizmo 2 and Gizmo 3.<br>This file is included by the Neuron C file                                       |

|            | ha_test.nc.                                                                                                                               |

| read.me    | A text file that contains updates to the documentation for the example host application that have occurred since it was printed.          |

**Read-Me Files.** The files ... MIP\README.TXT and ... \MIP\_DPS\README.TXT are text files with updates to the *MIP User's Guide* that have occurred since it was printed. The file ... \HA\READ.ME is a text file with updates to the *Host Application Programmer's Guide* that have occurred since it was printed. These example directories are the same as described above for the network driver source, and the sample host application.

### **Upgrading From Previous Releases**

The following procedure describes the upgrade process for users of previous releases of the MIP.

- 1 Install the MIP software as described under Software Installation Instructions earlier in this chapter. The new MIP software will overwrite any previous releases.

- 2 The MIP image in existing network interfaces does not have to be upgraded unless you want to take advantage of the performance improvements of this release. To upgrade the MIP image in existing network interfaces, rebuild the MIP image as described in Chapter 3, and install this new image on your network interfaces.

- 3 Existing network interface hardware designs do not have to be modified.

- 4 Existing network drivers do not have to be modified, unless you want to take advantage of the performance improvements in the new network driver example.

- 5 Existing host applications do not have to be modified, the network driver protocol for this release is fully compatible with previous releases.

# 3

# Creating a MIP Image

This chapter describes the process of building the MIP image that will be loaded onto a network interface.

# Writing the MIP Application

The *MIP image* is the firmware loaded on a network interface that enables the network interface to act as a LonTalk communications processor. The MIP image is made up of the following components:

- Neuron Chip firmware. The MIP image includes the standard Neuron Chip firmware that handles layers 1 5 and portions of layer 6 of the LonTalk protocol and controls the execution of the MIP firmware.

- **MIP firmware**. The MIP firmware includes functions that extend the Neuron Chip firmware by hooking into the layer 5 and 6 processing functions of the Neuron Chip firmware to enable portions of layers 6 and all of layer 7 to be moved to the host processor.

- **MIP** application. The MIP application is a Neuron C source program that specifies configuration options for the MIP and Neuron Chip firmware. The MIP application should only setup the hardware and call the MIP firmware. For the MIP/P50, the MIP application must also define an uplink interrupt request function. No other user code should be included. Once the MIP firmware is started, it never returns to the MIP application. The MIP application is different for the parallel MIPs (the MIP/P20 and MIP/P50) and the dual-ported MIP (the MIP/DPS). All three versions are described in the following sections.

The MIP image may be built to initially start-up in the configured or unconfigured state as described under the *Target Network Types and Firmware State Selection* section of the *LonBuilder User's Guide*, or in the Help information for the NodeBuilder Device Template Window Export tab (see the *NodeBuilder User's Guide*). Network interfaces that are shipped without host applications should be built to come up unconfigured to prevent network address conflicts when the network interface is first installed in a network.

#### Example MIP Application for the MIP/P20

The following is an example of a MIP application for the MIP/P20. This example is included with the LonBuilder MIP/P20 and MIP/P50 Developer's Kit in the mip\_ap20.nc file. This file is installed in the examples directory (the default directory is \LB\EXAMPLES\MIP or \LONWORKS\NB\EXA\MIP).

#pragma micro\_interface #pragma idempotent\_duplicate\_off

// Select explicit addressing on or off with this pragma.

#pragma explicit\_addressing\_on

// Select NEURON CHIP (on) or host (off) NV selection.

#pragma netvar\_processing\_off

// When NEURON CHIP NV selection is specified (on), the // set\_netvar\_count and num\_addr\_table\_entries pragmas are // used to control the amount of memory the NEURON CHIP uses // for the network variable configuration and address tables. #pragma set\_netvar\_count 13 #pragma num\_addr\_table\_entries 14

#pragma receive\_trans\_count 4

#pragma set\_id\_string "MIP"

```

// Modify the following pragmas to set buffer sizes and counts.

#pragma app_buf_out_count

2

#pragma app_buf_out_priority_count

0

#pragma net_buf_out_priority_count

0

#pragma app_buf_in_count

2

#pragma app_buf_out_size

66

#pragma app_buf_in_size

66

#pragma net_buf_out_size

66

66

#pragma net_buf_in_size

// Modify this declaration to suit your hardware interface.

IO_0 parallel slave p_bus;

extern void mip_p20_interface(unsigned long throttle);

when (reset) {

// The argument <throttle> will yield about 375

// microseconds of delay per count. A value of

// one yields no throttle.

mip_p20_interface(1);

}

```

#### Example MIP Application for the MIP/P50

The following is an example of a MIP application for the MIP/P50. This example is included with the LonBuilder MIP/P20 and MIP/P50 Developer's Kit in the mip\_ap50.nc file. This file is installed in the examples directory (the default directory is \LB\EXAMPLES\MIP or \LONWORKS\NB\EXA\MIP).

```

#pragma micro_interface

#pragma idempotent_duplicate_off

// Select explicit addressing on or off with this pragma.

#pragma explicit_addressing_on

// Select NEURON CHIP (on) or host (off) NV selection.

#pragma netvar_processing_off

#pragma set_id_string

"MIP"

// Modify the following pragmas to set buffer sizes and counts.

#pragma app_buf_out_count

3

#pragma app_buf_out_priority_count

3

7

#pragma app_buf_in_count

#pragma app_buf_out_size

66

#pragma app_buf_in_size

66

#pragma net_buf_out_size

66

#pragma net_buf_in_size

66

// Modify this declaration to suit your hardware interface.

IO_0 parallel slave p_bus;

// The argument <irqp> is a pointer to the Interrupt Callback

function.

11

// The argument <throttle> will yield about 350 microseconds

// of delay per count. A value of one yields no throttle.

```

#### Example MIP Application for the MIP/DPS

Following is an example of a MIP application for the MIP/DPS. This example is included with the MIP/DPS Developer's Kit in the mip\_dps.nc file. This file is installed in the examples directory (the default directory is \LB\EXAMPLES\MIP\_DPS or \LONWORKS\NB\EXA\MIP\_DPS).

```

#pragma warnings_off

#pragma micro_interface

#pragma idempotent_duplicate_off

// Select explicit addressing on or off with this pragma.

#pragma explicit_addressing_on

// Select NEURON CHIP (on) or host (off) NV selection.

#pragma netvar_processing_off

// Set RAM test to OFF

#pragma ram_test_off

// Places buffers in DP ram.

#pragma all_bufs_offchip

30

#pragma set_netvar_count

15

#pragma num_addr_table_entries

16

#pragma receive_trans_count

"DP_MIP"

#pragma set_id_string

#pragma app_buf_out_count

23

3

#pragma app_buf_out_priority_count

#pragma app_buf_in_count

23

66

#pragma app_buf_out_size

#pragma app_buf_in_size

66

#pragma net_buf_out_size

66

#pragma net_buf_in_size

66

// This allows pin IO_10 to drive an interrupt signal to the host,

// if needed.

IO_10 output bit irqp10 = 1;

// This allows pin IO_0 to be initialized as a message indicator.

IO_0 output oneshot invert clock (7) status_led = 1;

11

```

```

// Protoype for the MIP interface function. The <if_flush> argument

// will cause the MIP application to enter the INIT FLUSH state

// following reset. The <if_oba_ir> argument causes the host to be

// interrupted whenever a new output buffer is posted to the interface

// The <sema_base_page> argument is the 8 bit page address of the

// semaphore area.

//

extern void dpram_mip_interface(unsigned if_flush, unsigned

if_oba_ir,

unsigned short sema_base_page);

when (reset) {

// In this example the semaphore area is mapped to base 0x8000.

dpram_mip_interface(TRUE, TRUE, 0x80);

}

```

#### Specifying MIP Pragmas

The pragmas specified in the MIP application select the network interface configuration options defined in the LONWORKS Host Application Programmer's Guide. The sample MIP applications contain default values for these pragmas. Edit the MIP application source file to change them.

```

#pragma micro_interface

```

This pragma indicates to the compiler that this node is a network interface. This pragma also ensures that the MIP image will start execution even if it is not configured. This pragma must be specified for MIP applications.

```

#pragma idempotent_duplicate_off

#pragma idempotent_duplicate_on

```

These pragmas control the idempotent request retry bit in the application buffer. This bit corresponds to the addr\_mode bit of the ExpMsgHdr structure declared in ni\_msg.h for incoming request messages only. These pragmas only apply to MIP applications running on version 6 of the Neuron Chip firmware or newer. One of these pragmas must be specified. The idempotent\_duplicate\_on pragma should be specified unless the host application depends on the pre-version 6 firmware behavior of the idempotent request retry bit (i.e., it was always set to 0 prior to version 6 for incoming request messages).

If idempotent\_duplicate\_on is specified, the idempotent request retry bit indicates a duplicate request for incoming request messages. The host application will only receive the duplicate request if the response to the original request contained data. When a duplicate request is received, the host application can return the original response, or can provide a new updated response. See *Idempotent Versus Non-Idempotent Requests* in Chapter 4 of the *Neuron C Programmer's Guide* for more information.

If idempotent\_duplicate\_off is specified, or if the Neuron Chip firmware used in the network interface is a version prior to version 6, the idempotent request retry bit is always 0.

```

#pragma explicit_addressing_on

#pragma explicit_addressing_off

```

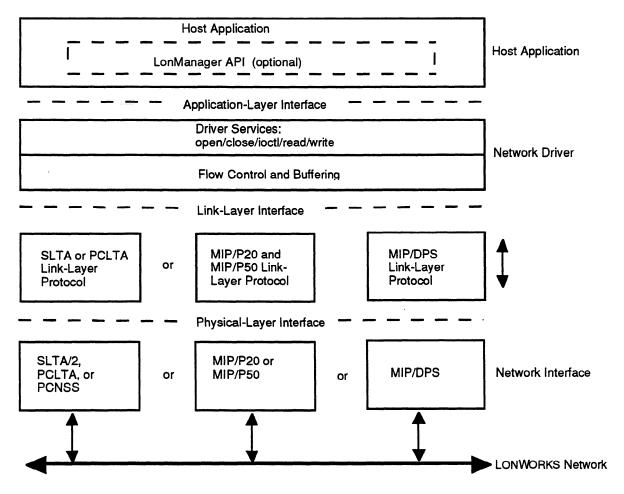

These pragmas determine whether space is set aside in the application buffer for explicit addressing information. The value in the sample MIP applications is explicit\_addressing\_on, which adds 11 bytes of overhead per application buffer for the explicit addressing information. Explicit addressing allows a host application to bypass the network interface's address table, allowing the host application to send LonTalk messages to an unlimited number of nodes. See the LONWORKS Host Application Programmer's Guide for more information. The default value is explicit\_addressing\_on. The explicit\_addressing\_on pragma must be specified for MIP applications to be used with the LonMaker<sup>™</sup> Installation Tool or the LonManager API.

```

#pragma netvar_processing_on

#pragma netvar_processing_off

```

These pragmas specify whether network variable selection is performed by the Neuron Chip firmware (network interface selection) or the host application (host selection). See the LONWORKS Host Application Programmer's Guide for a description of these options. When network interface selection (netvar\_processing\_on) is specified, the size of the network variable configuration table must be specified with the set\_netvar\_count pragma. The setting netvar\_processing\_off is the default. MIP applications must specify host selection (netvar\_processing\_off) to be used with the LonMaker Installation Tool or the LonManager API.

#pragma set\_netvar\_count nn

This pragma defines the size of the network variable configuration table when the netvar\_processing\_on (network interface selection) pragma is specified. The value of nn is the number of entries to be reserved for the table, and may be any value from 0 to 62. When the MIP/P20 is used on the Neuron 3120 Chip, the size of the network variable configuration table is limited by the amount of free memory in the Neuron 3120 Chip EEPROM. The number of entries can be traded off against the number of address table entries, but typical values for nodes configured for 1 and 2 domains are illustrated in table 4.1.

#pragma num\_addr\_table\_entries nn

This pragma specifies the number of address table entries to reserve in the MIP image. See the *Neuron C Programmer's Guide* for more information on the use of this pragma. When the MIP/P20 is used on the Neuron 3120 Chip, the size of the address table is limited by the amount of free memory in the Neuron 3120 Chip EEPROM. The number of entries can be traded off against the number of network variable configuration table entries, but typical values for nodes configured for 1 and 2 domains are illustrated in table 4.1. The default size is 15 entries.

#pragma one\_domain

This pragma limits the domain table to one entry. The default size is two entries. See the *Neuron C Programmer's Guide* for more information on the use of this pragma. When the MIP/P20 is used on a Neuron 3120 Chip, the number of entries can be traded off against the number of network variable configuration table entries and address table entries as shown in table 4.1.

```

#pragma ram_test_off

```

This pragma disables the standard RAM test that is performed by the Neuron Chip firmware during power-up initialization. This power-up test should normally be performed for network interfaces based on the MIP/P20 or MIP/P50, but may be disabled for network interfaces based on the MIP/DPS to prevent address conflicts with the host during power-up. Recommended usage is to leave the RAM test enabled for the MIP/P20 and MIP/P50; and disable the RAM test with ram\_test\_off for the MIP/DPS.

#pragma all\_bufs\_offchip

This pragma moves all application and network buffers to off-chip RAM. This pragma should be used with the MIP/DPS to ensure that the buffers are located in the dual-ported RAM. Recommended usage is to leave the buffers in their default locations for the MIP/P20 and MIP/P50; and move the buffers off-chip with all\_bufs\_offchip for the MIP/DPS.

#pragma set\_id\_string "string"

This pragma defines the program ID string contained in the MIP image. This string is sent in service pin messages, and is also sent in response to Query ID network management messages. The ID string should be changed in the MIP application source if the MIP image is only to be used with a single host application. If the MIP image will potentially be used with multiple host applications, the program ID can be left as a generic ID that is replaced by the host application when it starts running. The generic program IDs in the sample MIP applications are "MIP" for the MIP/P20 and MIP/P50; and "DP\_MIP" for the MIP/DPS.

When the MIP/P20 is used on the Neuron 3120 Chip, the size of the domain table, address table, and network variable configuration table is limited by the amount of free memory in the Neuron 3120 Chip EEPROM. Typical values for 3120-based nodes configured for 1 and 2 domains are illustrated in table 4.1. This table does not apply to the Neuron 3120E1 and 3120E2 Chips, which have more available EEPROM. When modifying the buffer sizes and counts, see the link map generated by the LonBuilder or NodeBuilder linker to determine the available EEPROM and RAM resources.

| Domains | Address Table<br>Entries | NV Configuration Table<br>Entries |

|---------|--------------------------|-----------------------------------|

| 1       | 8                        | 28                                |

| 2       | 15                       | 11                                |

Table 4.1 Table Size Trade-Offs for 3120-Based Network Interfaces

Additional pragmas are used to set Neuron Chip resources such as buffer counts and sizes, and receive transaction counts. The sample MIP applications for the MIP/P20 and MIP/P50 are set up to fit the buffers entirely within the Neuron Chip's on-chip RAM. The sample MIP application for the MIP/DPS is set up to fit the buffers within the default off-chip dual-ported RAM. The default sizes should be increased if large explicit messages will be used. The default counts should be increased if the host applications will cause too many messages to be lost due to unavailable buffers. Increased sizes or counts may require the use of off-chip RAM with the MIP/P50. For a complete descriptions of these pragmas, refer to Chapter 1 of the Neuron C Programmer's Guide.

The buffer size settings in the sample MIP applications assume explicit messaging and explicit addressing as defined in table 6.1 in the Neuron C Programmer's Guide. They are defined by pragmas and may be configured at run-time by writing to the application image. The Neuron Chip Data Book Appendix A describes the locations and encodings of these fields within the application image.

#### Declaring MIP I/O Objects

When using the MIP/P20 or MIP/P50, a parallel I/O object must be declared with the following statement:

IO\_0 parallel slave p\_bus; or IO\_0 parallel slave\_b p\_bus;

Select the first declaration for a slave A interface and the second declaration for a slave B interface. Slave A mode is suitable for parallel port interfaces; slave B mode requires fewer external components to interface to a memory bus. See the *Parallel I/O Interface to the Neuron Chip* engineering bulletin for a description of the operational characteristics of the parallel I/O functions including a description of the two slave modes and management of the token.

When using the MIP/DPS, an I/O object must be declared for the uplink interrupt, even if the I/O pin is not used. An optional I/O object may be declared for a message indicator output. The two I/O objects are declared with the following statements:

IO\_10 output bit irqp10 = 1; IO\_0 output oneshot invert clock (7) status\_led = 1;

Calling the MIP Function

When using the MIP/P20, the  $mip_p20_interface()$  function is called to invoke the MIP firmware. This function call never returns. The function prototype for this function is: extern void mip\_p20\_interface(unsigned long throttle);

The throttle parameter specifies the throttle delay in units of approximately 375  $\mu$ s at an input clock rate of 10 MHz. For example, a throttle parameter of 40 specifies approximately a 15 millisecond throttle with a 10 MHz input clock. The throttle delay scales with the input clock. A throttle of 1 specifies no throttle delay. See *Polled I/O* in Chapter 4 for more information on the throttle delay.

When using the MIP/P50, the mip\_p50\_interface() function is called to invoke the MIP firmware. This function call never returns. The function prototype for this function is:

The irqp parameter specifies the address of a user-supplied Neuron C function which is called when the MIP wishes to assert an uplink host interrupt.

The mip\_ap50.nc example MIP application described earlier in this chapter includes an example function to write a 1 (one) to location 0xC000 to request an interrupt. External hardware can decode this write to generate an interrupt signal.

The throttle parameter specifies the throttle delay in units of approximately 350 µs at an input clock rate of 10 MHz. A throttle parameter of 1 may be specified when the MIP/P50 uplink interrupt is used. In this case, the host driver will normally keep the write token when the network is in the idle state. If the host has some downlink traffic to send, it can immediately use the token to write it to the network interface. If the network interface has some uplink traffic, it can interrupt the host to indicate that the write token should be passed down. This provides optimum latency in both uplink and downlink directions. If the uplink interrupt is not implemented, the token will need to be continuously passed between the host and the network interface so that each will have an opportunity to pass traffic to the other. This will increase latency because delays to wait for the token may be necessary.

See Interrupt-Driven I/O in Chapter 4 for more information on the uplink interrupt. If an uplink interrupt is not required, supply the address of an empty function as the irqp parameter.

When using the MIP/DPS, the dpram\_mip\_interface function is called to invoke the MIP firmware. This function call never returns. The function prototype for this function is:

The if\_flush parameter specifies whether the MIP application will enter the FLUSH state after every reset. If if\_flush is TRUE, the MIP-based node will not be able to communicate on the network after a reset. The MIP application prevents communications by entering a FLUSH state. This state causes the MIP to ignore all incoming messages and prevents all outgoing messages, even service pin messages. This FLUSH state is provided to prevent any other network management tools from performing network management functions on the MIP-based node before the host has a chance to perform any of its own network management functions. This state is canceled with the niFLUSH\_CANCEL command from the host. A network driver for a MIP-based network interface may automatically

enable network communications when the network interface is opened by sending the niFLUSH\_CANCEL command when the driver is opened and when it receives an uplink message from the MIP application indicating that it has been reset. Alternatively, if the MIP application is built with if\_flush set to FALSE, the network interface will not enter the FLUSH state after each reset, and network communications will be immediately enabled.

The if\_oba\_ir parameter specifies whether the MIP application will post an uplink interrupt when it frees an output buffer. If if\_oba\_ir is FALSE, the MIP application posts an uplink interrupt whenever it has uplink traffic for the host (incoming message, incoming response, completion event, or network interface command). If if\_oba\_ir is TRUE, the MIP application will, in addition, post an uplink interrupt when it has freed a downlink application buffer. This occurs shortly after the host has read a completion event, which allows the MIP to free the corresponding buffer.

The sema\_base\_page parameter specifies the 8-bit page address of the semaphore area in the dual-ported RAM device. For example, a semaphore base page parameter of 0x80 specifies that the semaphores start at location 0x8000 in memory. See the *Implementing a MIP/DPS Network Driver* in Chapter 5 for more information on the use of semaphores.

# **Building the MIP Image**

The MIP image is built using the LonBuilder or NodeBuilder tools following the same procedure as any other node being built from Neuron C source code. This process is described in Chapters 6 and 7 of the LonBuilder User's Guide, and in Chapter 5 of the NodeBuilder User's Guide. The node build takes place as it would for any other node except that no binding can occur for network interfaces that have not been integrated with a host application.

Memory properties are defined for a MIP-based node as with any other node. The typical memory properties for each MIP are described in the following table:

| Memory Type | MIP/P20                      | MIP/P50                                                                                    | MIP/DPS                                                                                                                            |

|-------------|------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| ROM         | 0 (on a Neuron<br>3120 Chip) | 128 pages typical;<br>66 pages minimum *                                                   | 128 pages typical;<br>68 pages minimum                                                                                             |

| EEPROM      | 0                            | 0                                                                                          | 0                                                                                                                                  |

| RAM         | 0 (on a Neuron<br>3120 Chip) | 0 - 166 (required size must<br>be large enough for the<br>number of buffers<br>declared) * | 16 - 166 (required size must<br>be large enough for the<br>number of buffers declared)                                             |

| Ι/Ο         | 0                            | 1 page if memory-mapped<br>uplink interrupt is used *                                      | 1 page<br>(semaphore page; start<br>address must match the<br>sema_base_page parameter<br>in the call to<br>dpram_mip_interface()) |

|             |                              | * or 0 for a Neuron 3120E1 or<br>3120E2 Chip                                               |                                                                                                                                    |

Once a network interface is integrated with a host application, the host node can be bound to connections as described under *Binding to a Host Node* in Chapter 3 of the LONWORKS Host Application Programmer's Guide.

## Loading the MIP Image

Once the MIP image has been built, there are four methods to load the image into a network interface:

- Emulator download. If the network interface is initially prototyped on a LonBuilder Neuron Emulator, the MIP image can be loaded directly into the emulator memory using the LonBuilder Load command. When using the MIP/P20 or MIP/P50, the emulator will continuously watchdog reset if no host is present. To reliably load such a network interface, the host should be present and be exchanging tokens with the network interface. The MIP/DPS cannot be loaded on an emulator since the dual-ported memory cannot be emulated.

- Network download. If the MIP is to be loaded in read/write memory on the network interface such as the on-chip EEPROM, the MIP image can be loaded over the network using the LonBuilder or NodeBuilder Load command. When using the MIP/P20 or MIP/P50, the network interface will continuously watchdog reset if no host is present. To reliably load such a network interface, the host should be present and be exchanging tokens with the network interface.

- **PROM export**. When using any version of the MIP with a Neuron 3150 Chip, the MIP image can be exported to a ROM image using the LonBuilder or NodeBuilder Export command. The ROM image is loaded into a PROM using a PROM programmer.

- Neuron 3120 image export. When using the MIP/P20 with a Neuron 3120, 3120E1, or 3120E2 Chip, the MIP image must be exported to a Neuron 3120 image using the LonBuilder or NodeBuilder Export command. The Neuron 3120 image is loaded into a Neuron 3120, 3120E1, or 3120E2 Chip using a Neuron 3120 programmer such as the LONWORKS Neuron 3120 Programmer.

The MIP application may be exported to initially start-up in the configured or unconfigured state as described under the *Target Network Types and Firmware State Selection* section of the *LonBuilder User's Guide*, or in the Help information for the NodeBuilder Device Template Window Export tab (see Chapter 5 of the *NodeBuilder User's Guide*). Network interfaces that are shipped without host applications should be built to come up unconfigured to prevent network address conflicts when the network interface is first installed in a network.

Once reset, a MIP-based node will always start up online, and cannot start offline. Because of this, the LonBuilder Load command has the same effect as the LonBuilder Load/Start command, they both load and start the MIP-based node.

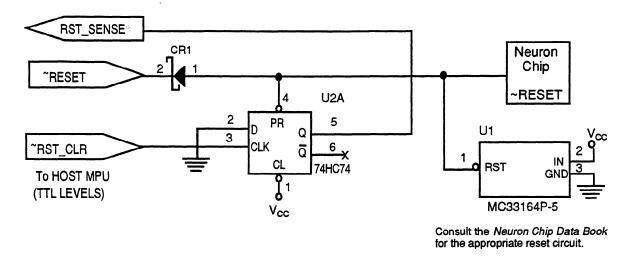

If the network interface will be loaded or configured over the network, the host must be able to sense when the network interface has been reset. See the discussion in Chapter 4, *Building a Network Interface*, for information on reset latch circuitry.

# 4

# Building a Network Interface

This chapter describes the process of building a network interface. A detailed discussion of host interface considerations is included.

## **Building Network Interface Hardware**

The network interface hardware is similar to any custom node containing a Neuron Chip, a transceiver, and memory. The hardware itself is built the same way as you build a custom node. Refer to the LONWORKS Custom Node Development engineering bulletin for additional information. Network interfaces based on the MIP/P20 or MIP/P50 may be based on LONWORKS control modules which conveniently integrate the Neuron Chip, transceiver, memory, and support circuitry. LONWORKS control modules cannot be used with the MIP/P50 when using uplink interrupts, and also cannot be used with the MIP/DPS.

The network interface external interface file (.XIF extension) is exported as with any custom node. The network interface external interface file does not contain network variable records. Host application network variables can be manually added to the external interface file. Refer to the LonBuilder User's Guide or the NodeBuilder User's Guide for information on exporting external interface files. See Appendix B of the LONWORKS Host Application Programmer's Guide for a description of how to modify the external interface file to add network variables and message tags.

Network interfaces based on the MIP/P20 or MIP/P50 may be tested on a LonBuilder Neuron Emulator, or the LTM-10 LonTalk Node prior to building custom hardware. Because of the requirement for dual-ported memory, the MIP/DPS cannot be tested on an emulator or an LTM-10 Node and must be run on a custom node.

There are up to four hardware interfaces between a host and network interface. These interfaces are:

- *Host interface*. A data interface for transferring commands and data between the host and network interface.

- **Uplink interrupt**. An optional interrupt interface so that the network interface can interrupt the host when an uplink message buffer is available.

- **Reset latch**. An optional interface so that the host can be informed that a reset has occurred on the network interface. This interface is required for host-based nodes that will be reset, configured, or loaded over the network.

- Semaphores. Hardware semaphores shared by the host and network interface. Used for resource contention for the dual-ported RAM by the MIP/DPS. Not used for the MIP/P20 or MIP/P50.

The following sections describe these four hardware interfaces.

## **Building the Host Interface**

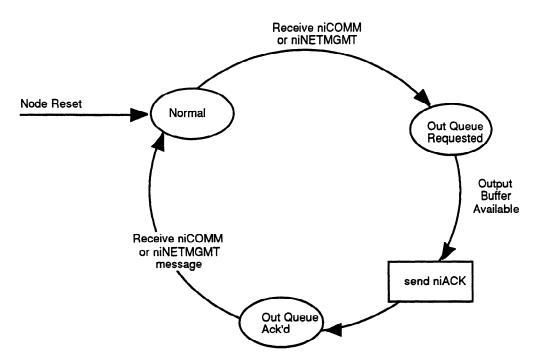

The host interface provides a communications path for transferring commands and data between the host and network interface. For the MIP/P20 and MIP/P50, the interface is an 11-bit parallel I/O interface. For the MIP/DPS, the interface is a dual-ported RAM with semaphores. Figures 1.1 through 1.3 illustrate the components of a network interface based on the MIP/P20, MIP/P50, and MIP/DPS.

#### MIP/P20 and MIP/P50 Host Interface

The MIP/P20 and MIP/P50 host interface is implemented as described in the *Parallel I/O Interface to the Neuron Chip* engineering bulletin and Chapter 8 of the *Neuron C Reference Guide*. The host must have the ability to execute the token passing algorithm required by the parallel I/O interface. This algorithm is implemented by the sample DOS network driver described in Chapter 5.

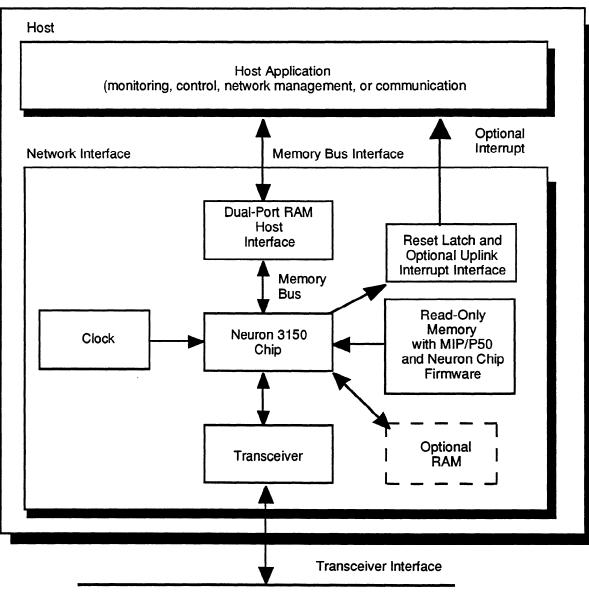

The MIP/P20 and MIP/P50 can be used with either of the two parallel I/O modes: slave A and slave B. The slave A mode is used to communicate with a parallel port. In slave A mode, the master (the host) and slave (the Neuron Chip) communicate through eight data lines, plus chip select, read/write, and handshake control lines.

The slave B mode is used to communicate with a memory or I/O bus. It is logically similar in operation to the slave A mode, however, the handshaking process and the data bus control are specifically tailored for use in a bus environment. Multiple slaves may reside on the same bus, as may other non-slave devices such as memory or other I/O devices. Slave B mode requires the host to alternatively select the data register and control register of the network interface in order to monitor the handshake bit. See the *Neuron Chip Data Book* for a comparison of these two modes.

Figure 4.1 illustrates the parallel I/O modes as used by the MIP/P20 and MIP/P50.

Figure 4.1 MIP/P20 and MIP/P50 Parallel I/O Modes

The host should not read the EOM at the parallel I/O interface level. Refer to the *Parallel I/O Interface to the Neuron Chip* engineering bulletin, which describes the purpose of the EOM step. The EOM is written in order to set up the HANDSHAKE signal for the next read operation.

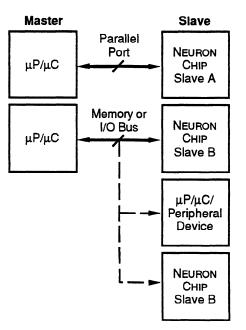

Figure 4.2 illustrates the use of the slave A mode of the MIP/P20 or MIP/P50 for interfacing the Neuron Chip to a Motorola 68HC11 microcontroller. The 68HC11 is the master and the Neuron Chip is the slave connected to the B and C ports of the 68HC11. The interface circuitry is considerably more involved than the slave B mode interface, which is shown in figure 4.3. See the next section on *Handling Uplink Requests* for other options for generating an uplink interrupt.

Figure 4.2 Sample Slave A Mode 68HC11 Interface for the MIP/P20 or MIP/P50

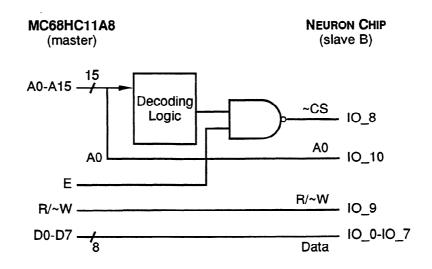

Figure 4.3 illustrates the use of the slave B mode of the MIP/P20 or MIP/P50 for interfacing the Neuron Chip to a Motorola 68HC11 microcontroller. The 68HC11 is the master and the Neuron Chip is the slave residing in the 68HC11's address space. No interface circuitry is needed aside from some address decoding logic that allows the 68HC11 to access the Neuron Chip by using specific addresses (one address for the data register and one for the control register).

Figure 4.3 Sample Slave B Mode 68HC11 Interface for the MIP/P20 and MIP/P50

If the host to Neuron Chip connection involves any type of external cabling, the data and control signals must be adequately conditioned, in particular the ~CS (chip select) signal. Crosstalk and poor rise times on this signal will interfere with the operation of the parallel I/O protocol.

#### MIP/DPS Host Interface

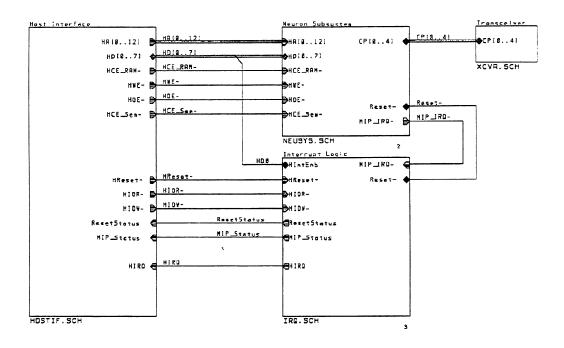

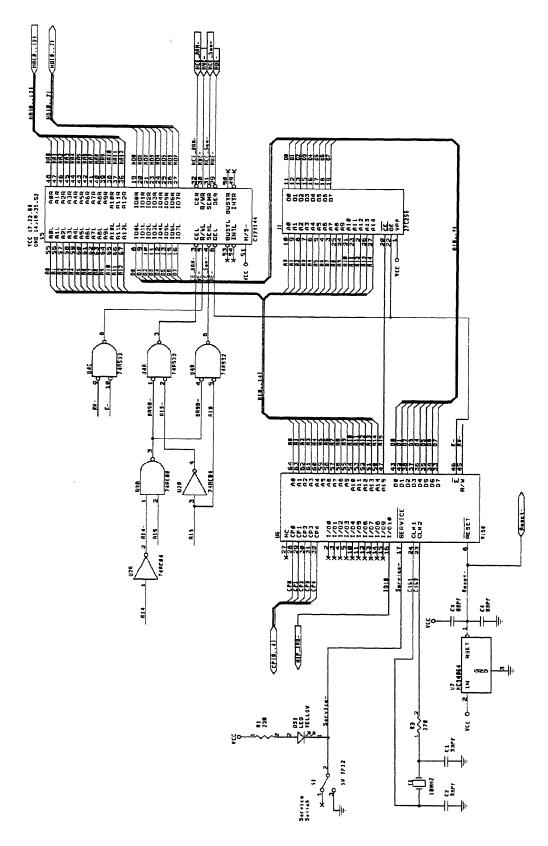

For the MIP/DPS, any dual-ported RAM can be used that supports the memory access requirements of the Neuron Chip and implements semaphores as described later in this chapter under *Implementing Semaphores*. Two dual ported RAMs that meet these requirements are the IDT 71342 and the Cypress 78144. The memory must be contiguous and start on a 256-byte page boundary. The starting address must be after the end of the ROM memory used for the MIP image, however the ROM and the dual-ported RAM do not have to be contiguous. The starting address and size of the RAM must be specified as external RAM in the LonBuilder Hardware Properties window or the NodeBuilder device template. Appendix B provides a sample schematic for a network interface based on the MIP/DPS.

### Handling Uplink Requests

There are two methods that the host can use to initiate the transfer of a message uplink from the network interface to the host: polled I/O and interrupt-driven I/O. Polled I/O is simpler, but requires that the host periodically check for the availability of an uplink message from the network interface. Interrupt driven I/O is more complex, but provides for asynchronous notification of the host when a message is ready to be transferred uplink. Either method can be used with any of the MIPs, but use of interrupt-driven I/O is more complex with the MIP/P20 (the MIP/P50 and MIP/DPS directly support uplink interrupts).

Once an uplink transfer is started with the MIP/P20 or MIP/P50, each byte of the message may also be transferred using polled I/O or interrupt-driven I/O. In addition, for the MIP/P50 using an uplink interrupt, a DMA (direct memory

Microprocessor Interface Program User's Guide

access) controller can be used to finish transferring the message. Polled I/O should be used once the transfer has started if the host's interrupt service processing time is long compared to the interrupt period. For example, the interrupt period is  $2.4\mu$ s for the MIP/P20 or MIP/P50 running at 10 MHz.

The MIP/DPS first writes an uplink message into one of the available uplink buffers in the dual-port RAM and then generates an uplink interrupt. Therefore no polled I/O is required for the MIP/DPS for each byte of an uplink packet.

#### Polled I/O

For polled I/O, the host network driver software periodically polls the network interface to determine if a message is available for an uplink transfer. The method of polling depends on which MIP is being used, and the interface mode of the MIP:

- *MIP/P20, slave A mode*. The handshake pin indicates that the MIP is ready to pass back the parallel interface token. The token may be part of a message packet, or may be a null token.

- MIP/P20, slave B mode. The handshake bit of the status port indicates that the MIP is ready to pass back the parallel interface token. The token may be part of a message packet, or may be a null token.

- MIP/P50, slave A or B mode. When the Neuron Chip running the MIP/P50 firmware does not own the write token, it will call the user-supplied uplink interrupt request routine to indicate that a message is available for an uplink transfer. This routine typically writes to a memory-mapped location, and external hardware decodes and latches this memory write. The address of the user-supplied uplink interrupt request function is specified in the call to the MIP function as described under *Calling the MIP Function* in Chapter 3. Alternatively, the handshake pin in slave A mode or the handshake bit in slave B mode can be used as with the MIP/P20. However, the handshake signal is asserted once per byte transferred. The memory-mapped I/O port is written once per uplink transfer request.

- **MIP/DPS**. The MIP/DPS firmware changes a state variable in the control interface structure in shared memory to indicate that a message is available for an uplink transfer. The control interface structure is described under *Control Interface Structure* in Chapter 5.

#### Interrupt-Driven I/O

For interrupt-driven I/O, an interrupt signal generated by the network interface informs the host that a message is available for an uplink transfer from the network interface to the host. The source of the interrupt depends on which MIP is being used:

• **MIP/P20**. Slave A mode should be used if an uplink interrupt is desired with the MIP/P20 since interrupts are difficult to generate with slave B mode. In slave A mode, the handshake pin interrupts the host every time the MIP is ready to pass back the parallel interface token. The token may be part of a LonTalk message packet from the network, a local network interface command, or a null token. The handshake pin therefore acts as both an uplink interrupt and a null token interrupt. However, the handshake signal is asserted once per byte

transferred. The host must transfer the packet to determine if it is a message or a null token.

MIP/P50. The MIP/P50 firmware calls the user-supplied uplink interrupt request function to generate an uplink interrupt. This routine typically writes to a memory-mapped location (which requires a Neuron 3150 Chip), and external hardware decodes and latches this memory write. This method is illustrated by the example MIP application in Chapter 3. The address of the user-supplied uplink interrupt request function is specified in the call to the MIP function as described under *Calling the MIP Function* in Chapter 3. The uplink interrupt signals an uplink LonTalk message from the network or a local network interface command. Either slave A or slave B mode may be used. In this model the host normally has the write token. Downlink transfers occur as needed. Uplink transfers occur via two interrupts from the network interface hardware. The first interrupt is a signal that the network interface does not own the token, and needs to send data uplink. The driver then writes downlink, giving up the token. The second interrupt is a signal that the network interface is starting an uplink transfer. In this case the driver reads the uplink data from the network interface. Both interrupts appear on a single interrupt request line since they are generated in the same manner by the network interface hardware. The distinction between them is made by evaluating the token state of the driver. No polling occurs in this model; it is completely interrupt-driven in the uplink transfer case.

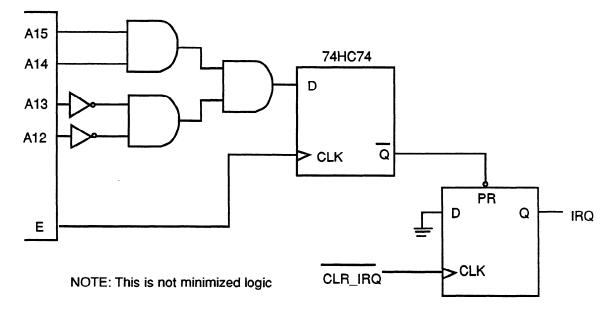

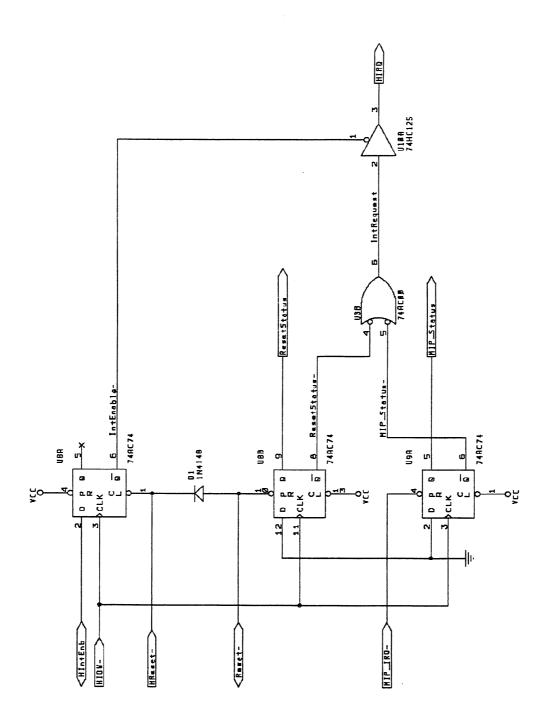

The following figure describes one method of generating the uplink interrupt using the example interrupt request function from Chapter 3. The address that is decoded is 0xC000. The upper four bits only of the address (1100) are decoded, therefore nothing else should be in the memory map from 0xC000 to 0xCFFF. As described in the *LTM-10 User's Guide*, similar hardware is implemented on the LTM-10 module, so that an -IRQ output is available from the module.

IRQ signals the host system that an uplink message is waiting. The host's interrupt subroutine <u>will</u> acknowledge the interrupt by briefly asserting ~CLR\_IRQ.

Figure 4.4 MIP/P50 Uplink Interrupt Generation for Interrupt-driven I/O

After the command byte is received with the uplink interrupt, if the command specifies a message, the length byte is read using polled I/O. Now that the length of the rest of the message is known, the transfer can be completed by polled I/O, interrupt I/O, or a DMA controller. When DMA is used, a separate end-of-transfer interrupt is generated by the DMA controller to signal to the driver that the transfer has been completed. Depending upon the host this driver is being used on, this may or may not be a faster way than using interruptdriven I/O, as setting up the DMA hardware usually entails a fair amount of overhead. Generally, larger-sized messages will achieve a greater performance improvement than small messages.

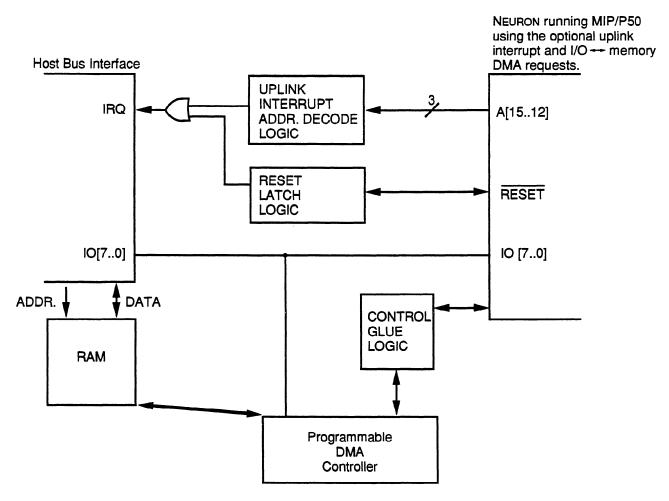

Figure 4.5 provides a block diagram of using interrupt I/O and a DMA channel with the MIP/P50.

Figure 4.5 MIP/P50 Interrupt I/O with DMA Functional Block Diagram

• **MIP/DPS.** The MIP/DPS firmware asserts IO\_10 low for 10 µs to generate an uplink interrupt. The IO\_10 pin can be used directly to generate an interrupt on the host. The IO\_10 pin should be latched if a latching interrupt is required by the host hardware. The uplink interrupt signals an uplink LonTalk message from the network or a local network interface command. The example MIP/DPS schematic in Appendix B includes an interrupt latch.

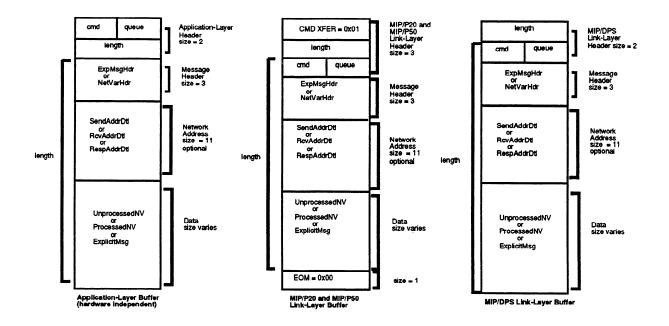

## Implementing a Reset Latch

The host must respond to any resets that occur on the network interface. For example, a network interface may be reset during the loading process to start execution with a new network image or application image. If the host ignores the reset, the load may fail and the host application will not operate.

For the MIP/P20 and the MIP/P50, the host must reinitiate the parallel interface token passing protocol after a reset occurs since the master is assumed to have the token after a Neuron Chip reset.

For the MIP/DPS, the host must terminate all writes to the shared memory and release any semaphores since the MIP/DPS firmware initializes the shared memory after a reset and rebuilds the control structures (see *Implementing Semaphores* below). The host must also terminate any reads after a reset since the data may no longer be valid.

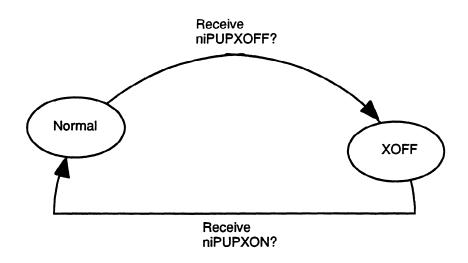

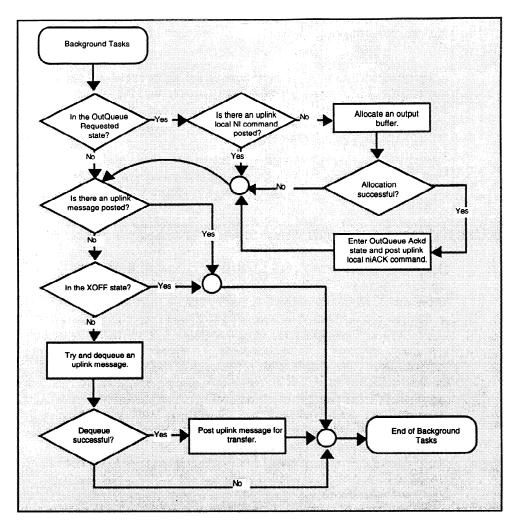

Once the MIP/DPS initialization has completed, the control\_iface.out and control\_iface.out\_p structures will be filled in with valid (non-null) pointers. The host will be informed that the reset initialization has been completed by an uplink interrupt for an uplink niRESET command. The niRESET command will be posted at control\_iface.command\_in. Once the niRESET command has been transferred uplink, the host may proceed with normal operation of the network interface. The MIP/DPS will be in the FLUSH state (no network messages allowed, in or out) until canceled with the niFLUSH\_CANCEL command from the host.