# Using the LONWORKS PLT-22 Power Line Transceiver in European Utility Applications

(70kHz – 95kHz Operation)

Version 1

Corporation

078-0180-01A

Echelon, LON, LONWORKS, LonBuilder, NodeBuilder, LonManager, LonTalk, LONMARK, Neuron, 3120, 3150, the LonUsers logo, the LONMARK logo, and the Echelon logo are trademarks of Echelon registered in the United States and other countries. LonPoint, LonSupport, and LonMaker are trademarks of Echelon Corporation.

Other brand and product names are trademarks or registered trademarks of their respective holders.

Neuron Chips, Power Line products, and other OEM Products were not designed for use in equipment or systems which involve danger to human health or safety or a risk of property damage, and Echelon assumes no responsibility or liability for use of the Neuron Chips or Power Line products in such applications.

Parts manufactured by vendors other than Echelon and referenced in this document have been described for illustrative purposes only and may not have been tested by Echelon. It is the responsibility of the customer to determine the suitability of these parts for each application.

ECHELON MAKES AND YOU RECEIVE NO WARRANTIES OR CONDITIONS, EXPRESS, IMPLIED, STATUTORY OR IN ANY COMMUNICATION WITH YOU, AND ECHELON SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Echelon Corporation.

Printed in the United States of America. Copyright ©1996 - 1999 by Echelon Corporation.

Echelon Corporation 4015 Miranda Avenue Palo Alto, CA 94304, USA www.echelon.com

## **Contents**

| 1 | Introduction Audience                                                   | 1-1<br>1-5 |

|---|-------------------------------------------------------------------------|------------|

|   | Content                                                                 | 1-5<br>1-5 |

|   | Related Documentation                                                   | 1-5        |

|   | Telatica Bodamentation                                                  | 1-0        |

| 2 | Using the PLT-22 Transceiver                                            | 2-1        |

|   | Mechanical Dimensions                                                   | 2-2        |

|   | PLT-22 Transceiver Pinout                                               | 2-3        |

|   | PLT-22 Transceiver Electrical Specifications                            | 2-4        |

|   | External Components                                                     | 2-6        |

|   | Crystal                                                                 | 2-6        |

|   | Power Supply Bypassing and Grounding                                    | 2-6        |

|   | Band-in-Use (BIU) and Packet Detect (PKD) LED Connections               | 2-7        |

|   | Neuron <sup>®</sup> Chip Connections                                    | 2-8        |

|   | Transmit Output Level                                                   | 2-9        |

|   | TXON Output Signal                                                      | 2-9        |

|   | Application Schematic: Neuron 3150® Chip                                | 2-10       |

|   | Application Schematic: Neuron 3120 <sup>®</sup> Chip                    | 2-11       |

| 3 | PLT-22 Transceiver Programming                                          | 3-1        |

|   | Dual Carrier Frequency Mode                                             | 3-2        |

|   | CENELEC Access Protocol                                                 | 3-2        |

|   | Power Management                                                        | 3-2        |

|   | Standard Transceiver Types                                              | 3-4        |

|   | LonBuilder <sup>®</sup> and NodeBuilder <sup>®</sup> PLT-22 Transceiver |            |

|   | Channel Definitions                                                     | 3-4        |

|   |                                                                         |            |

| 4 | Coupling Circuits                                                       | 4-1        |

|   | Power Line Communications                                               | 4-2        |

|   | Coupling Techniques                                                     | 4-4        |

|   | Power Line Coupling Basics                                              | 4-4        |

|   | Power Line Coupling Details                                             | 4-5        |

|   | Safety Issues                                                           | 4-8        |

|   | Safety Isolation Considerations                                         | 4-8        |

|   | 3 Phase AC Mains Circuits                                               | 4-10       |

|   | Capacitor Charge Storage                                                | 4-11       |

|   | Line Surge Protection                                                   | 4-11       |

|   | Fuse Selection                                                          | 4-13       |

|   | Recommended Coupling Circuit Schematics                                 | 4-13       |

|   | Example 1: A-Band, Line-to-Neutral, Non-Isolated Coupling               |            |

|   | Circuit                                                                 | 4-14       |

|   | Example 2: A-Band, Line-to-Neutral, Transformer-Isolated                       |                   |

|---|--------------------------------------------------------------------------------|-------------------|

|   | Coupling Circuit                                                               | 4-16              |

|   | Example 3: A-Band, Line-to-Neutral Three-Phase                                 |                   |

|   | Transformer-Isolated Coupling                                                  | 4-18              |

| 5 | Power Supplies for the PLT-22 Transceiver                                      | 5-1               |

|   | Introduction                                                                   | 5-2               |

|   | Power Supply Design Considerations                                             | 5-2               |

|   | Power Supply-Induced Attenuation                                               | 5-2               |

|   | Power Supply Noise                                                             | 5-3               |

|   | Energy Storage Power Supplies                                                  | 5-3               |

|   | Energy Storage Capacitor-Input Power Supplies                                  | 5-5               |

|   | Capacitor-Input Power Supply Schematic                                         | 5-7               |

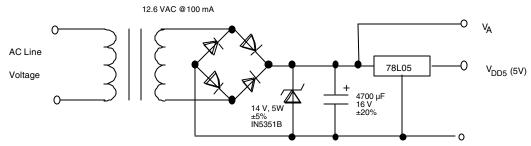

|   | Energy Storage Linear Supplies                                                 | 5-8               |

|   | Traditional Linear Power Supplies                                              | 5-9               |

|   | Switching Power Supplies                                                       | 5-9               |

|   | Power Supply-Induced Attenuation                                               | 5-9               |

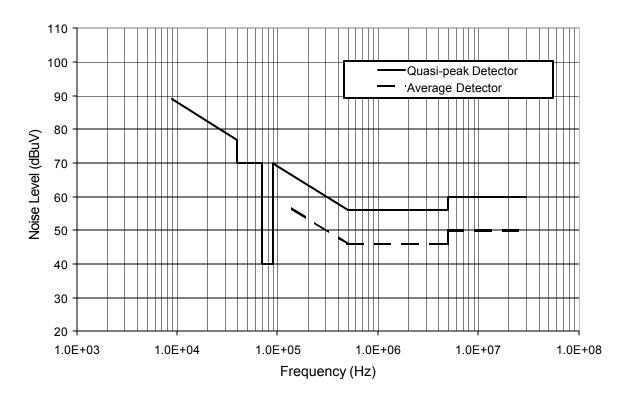

|   | Noise at the Power Supply Input                                                | 5-12              |

|   | Switching Power Supply Frequency Selection                                     | 5-12              |

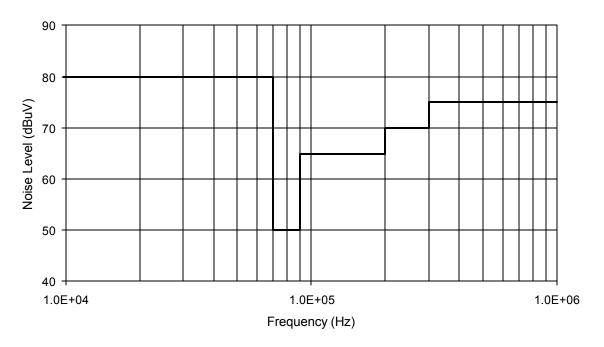

|   | Switching Power Supply Input Noise Masks                                       | 5-12              |

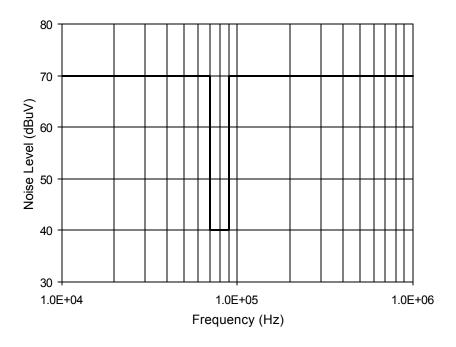

|   | Switching Power Supply Output Noise Masks                                      | 5-16              |

|   | Options  Declarize of Spritching Securities                                    | 5-18              |

|   | Pre-designed Switching Supplies                                                | 5-18              |

|   | Off-the-Shelf Switching Supplies Custom Switching Supplies                     | 5-18<br>5-19      |

|   |                                                                                |                   |

| 6 | Design and Test for Electromagnetic Compatibility                              | <b>6-1</b><br>6-2 |

|   | EMI Design Issues  Designing Systems for EMC (Floatromagnetic Compatibility)   | 6-2               |

|   | Designing Systems for EMC (Electromagnetic Compatibility)<br>ESD Design Issues | 6-4               |

|   | Designing Systems for ESD Immunity                                             | 6-4               |

|   | Conducted Emissions Testing                                                    | 6-6               |

|   |                                                                                | 0 0               |

| 7 | Communication Performance Verification                                         | 7-1               |

|   | Why Verify Communication Performance?                                          | 7-2               |

|   | Verification Strategy                                                          | 7-2               |

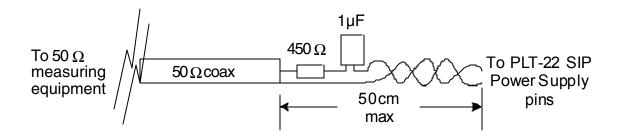

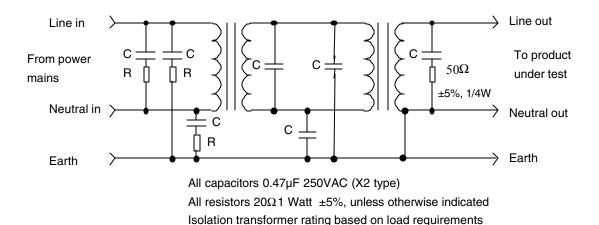

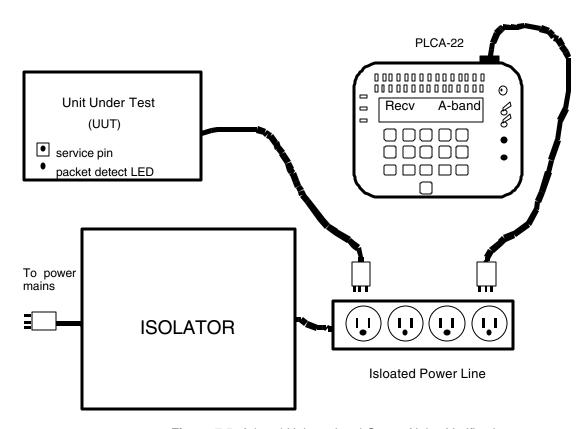

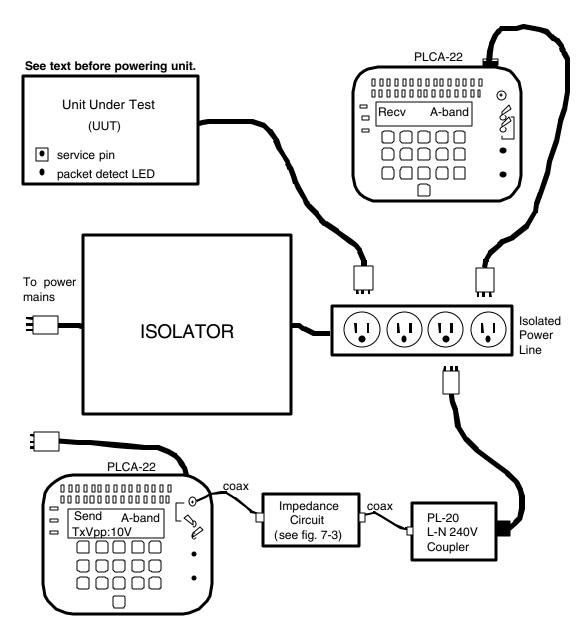

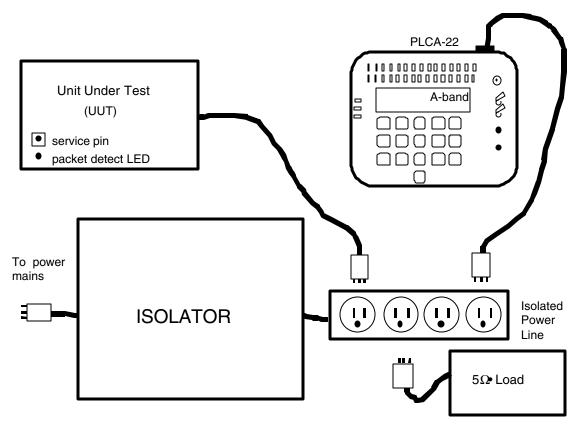

|   | Power Line Test Isolator                                                       | 7-3               |

|   | Test Equipment                                                                 | 7-4               |

|   | Good Citizen Verification                                                      | 7-5               |

|   | Unintentional Output Noise Verification                                        | 7-5               |

|   | Excessive Loading Verification                                                 | 7-7               |

|   | Transmit Performance Verification                                              | 7-9               |

|   | Receive Performance Verification                                               | 7-10              |

|   | Packet Error Measurement with Nodeutil Verification Procedure                  | 7-10              |

|   | vernication rrocedure                                                          | 7-11              |

| 8 | References                                                                     | 8-1               |

|   | Reference Documentation                                                        | 8-2               |

ii Echelon

| Appendix A Single Phase Isolation Transformer Specifications          | A-1 |

|-----------------------------------------------------------------------|-----|

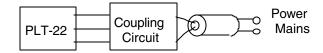

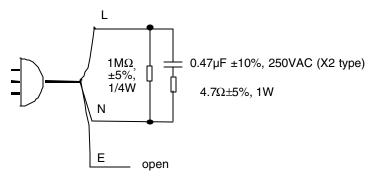

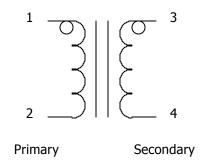

| PLT-22 Transceiver Isolation Transformer Schematic                    | A-2 |

| PLT-22 Transceiver Isolation Transformer Electrical<br>Specifications | A-2 |

| PLT-22 Transceiver Isolation Transformer Vendors                      | A-3 |

| Appendix B Three Phase Isolation Transformer Specifications           | B-1 |

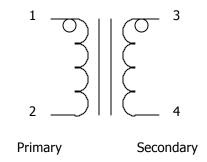

| PLT-22 Transceiver Isolation Transformer Schematic                    | B-2 |

| PLT-22 Transceiver Isolation Transformer Electrical<br>Specifications | B-2 |

| PLT-22 Transceiver Isolation Transformer Vendors                      | B-3 |

| Appendix C PLT-22 Transceiver-Based Node Checklist                    | C-1 |

| PLT-22 Transceiver-Based Node Checklist                               | C-2 |

| PLT-22 Transceiver and Neuron Chip Connections                        | C-2 |

| PLT-22 Transceiver Programming                                        | C-4 |

| PLT-22 Transceiver Coupling Circuit General                           | C-4 |

| PLT-22 Transceiver Coupling Circuit Components Key                    | C-5 |

| Specifications                                                        |     |

| PLT-22 Transceiver Power Supply - General                             | C-7 |

| PLT-22 Transceiver Power Supply - Switching Type                      | C-7 |

| EMI & ESD Design                                                      | C-8 |

| Product Qualification - EMC                                           | C-8 |

| Product Qualification - Electromagnetic Immunity and                  | C-8 |

| Communication Performance                                             |     |

iv Echelon

1

#### Introduction

The PLT-22 Power Line Transceiver provides a simple, cost-effective method of adding LonWorks® power line technology to utility automation systems. Network data are broadcast through the power mains, eliminating the need for dedicated wiring and greatly reducing installation costs. With selection of the appropriate external components, the PLT-22 transceiver can be configured to operate in the CENELEC Utility band (A-band). Operating in this band, the PLT-22 transceiver provides longer operating distances and greater reliabity than other utility band transceivers including the Echelon PLT-30. This Manual provides detailed guidelines for the use of the PLT-22 transceiver in the European Utility Band. For all other PLT-22 applications refer to the Lonworks PLT-22 Power Line Transceiver User's Guide (110kHz-140kHz operation).

Intermittent noise sources, impedance changes, and attenuation make the power line a hostile signal path. The PLT-22 transceiver operates reliably in this harsh environment through a novel dual carrier frequency capability as well as custom digital signal processing which provides adaptive carrier and data correlation, impulse noise cancellation, tone rejection, and low-overhead error correction. These innovations permit the transceiver to operate reliably in the presence of a wide variety of interference sources.

When used in the CENELEC utility band, the PLT-22 transceiver operates as a non-backward-compatible replacement for the previous generation PLT-30 power line transceiver. The PLT-22 transceiver provides compelling advantages over the PLT-30 transceiver in terms of bit rate, price, performance, and size. The PLT-22 transceiver complies with European CENELEC EN 50065-11 regulations for signaling in the 9kHz-to-95kHz frequency band (A-band).

With its dual carrier frequency capability, PLT-22 based-nodes are able to communicate even when the primary carrier frequency range is blocked by noise. If impairments prevent communication in this frequency range, the PLT-22 node will automatically switch carrier frequencies in order to complete the transaction with other PLT-22 based nodes.

The transceiver's power amplifier produces an output of 7V p-p for maximum communication performance. The  $1\Omega$  output impedance and 1A p-p current capability of the amplifier allow it to drive high output levels and low impedance circuits, while the highly efficient design draws significantly less current than previous transceivers.

The PLT-22 transceiver is powered by user-supplied +11.4 to +16VDC and +5VDC power supplies. The wide supply range is a key benefit when designing inexpensive power supplies. If a battery-backed power supply is used, the transceiver will continue signaling even during a power failure on the power mains.

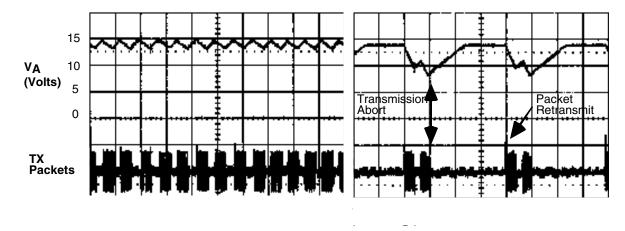

The PLT-22 transceiver incorporates a power management feature that constantly monitors the status of the node's power supply. If during transmission the power supply voltage falls to a level that is insufficient to ensure reliable signaling, the transceiver tells the Neuron Chip to stop transmitting until the power supply voltage rises to an acceptable level. This allows the use of a power supply with 1/3 the current capacity otherwise required (100mA versus 300mA). The net result is a reduction in the size, cost, and thermal dissipation of the power supply. Power management is especially useful for high volume, low cost applications.

The PLT-22 transceiver is supplied as a miniature uncoated Single In-Line Package (SIP) which can be mounted on or inside an OEM product, directly adjacent to the Neuron Chip with which it is used. The PLT-22 transceiver is not a drop-in replacement for the previous generation PLT-30 transceiver; however, similarity of pinout allows a circuit board to be laid out with minimal disturbance to other circuits. In addition, a PLT-22 based design is significantly smaller than a PLT-30 based design, allowing it to easily fit into existing enclosures.

The transceiver communicates at a raw bit rate of 3.6kbps and has a maximum packet rate of 13 packets per second. This high throughput makes the transceiver well suited for utility automation applications.

For applications in utility substations, the PLT-22 transceiver can be used with Echelon's PLA-21 Power Line Amplifier. Capable of transmitting a signal with 2Ap-p

current drive, the PLA-21 amplifier is ideal for driving multiple phase coupling circuits, high attenuation power circuits, and very low impedance loads near distribution transformers.

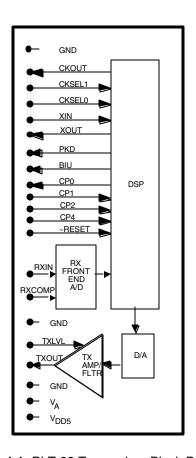

Figure 1.1 PLT-22 Transceiver Block Diagram

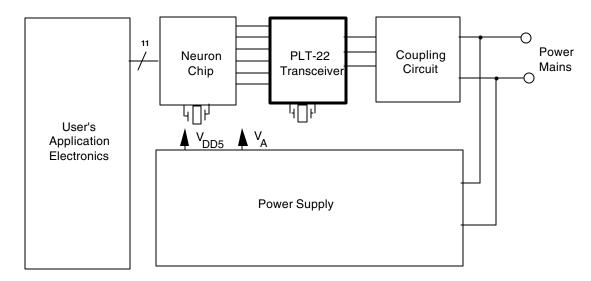

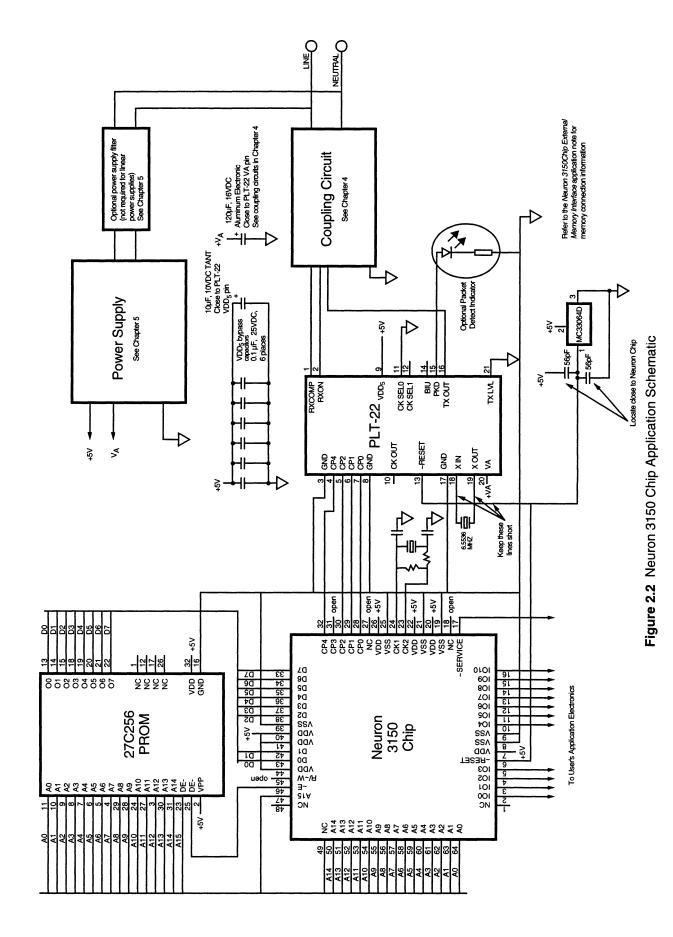

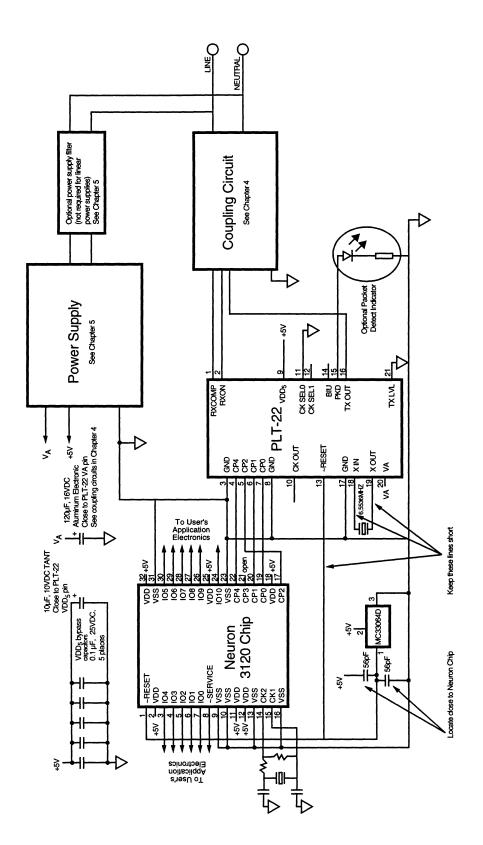

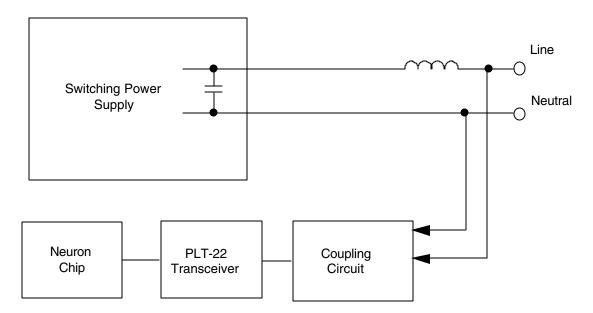

The compact PLT-22 transceiver must be mounted using hand or wave soldering and requires only the addition of a Neuron 3120<sup>®</sup> Chip or Neuron 3150<sup>®</sup> Chip, two crystals, power line coupling network, power supply, and application electronics to build a complete node (figure 1.2).

Figure 1.2 Typical PLT-22 Transceiver-Based Node

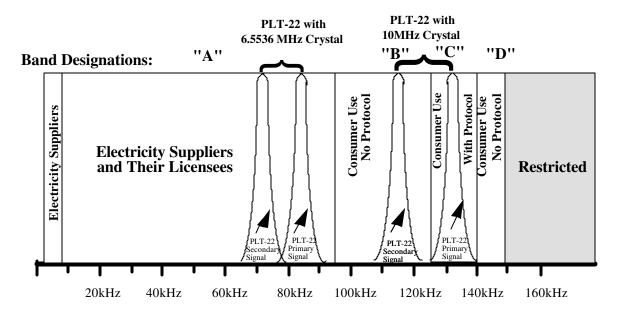

Under CENELEC EN 50065-1 "Signaling on low-voltage electrical installations in the frequency range 3kHz to 148.5kHz" Part 1 "General requirements, frequency bands and electromagnetic disturbances," communication frequencies are allocated as shown in figure 1.3. When used with a 6.5536MHz crystal, both the primary and secondary operating frequencies of the PLT-22 transceiver are within the CENELEC A-band.

Figure 1.3 CENELEC Frequency Allocation

#### **Audience**

This document is intended for designers of products using the PLT-22 Power Line Transceiver in the CENELEC utility band (A-band).

#### Content

This manual provides detailed operating instructions for the use of the PLT-22 transceiver in the CENELEC utility band.

#### **Related Documentation**

The following documents are suggested reading:

PLT-22 Power Line Transceiver data sheet (003-0250-01)

PLCA-22 Power Line Communication Analyzer User's Guide (078-0147-01)

LONWORKS Custom Node Development (005-0024-01)

$LONMARK^{\textcircled{R}}Layers~1\text{-}6~Interoperability~Guidelines}~~(078\text{-}0014\text{-}01)$

LONMARK Application Layer Interoperability Guidelines (078-0120-01)

Neuron Chip Data Book as published by Motorola and Toshiba

2

# Using the PLT-22 Transceiver

This chapter describes the electrical characteristics of the PLT-22 transceiver when used in the CENELEC utility band (A-band). Interface circuit requirements and application schematics for A-band use are also included.

#### **Mechanical Dimensions**

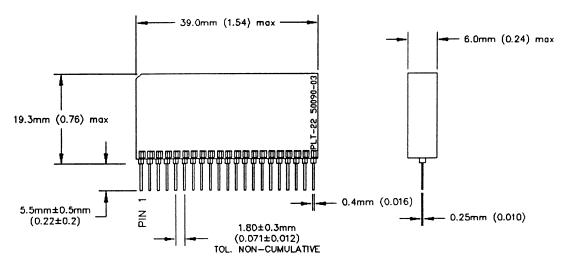

Figure 2.1 presents the mechanical dimensions of the PLT-22 transceiver.

The PLT-22 is produced as an uncoated SIP (in contrast to the coated PLT-10A, and PLT-30 transceivers).

CONTROLLING DIMENSIONS: MILLIMETERS (INCHES ARE SHOWN IN PARENTHESES AND ARE ROUNDED OFF.)

Figure 2.1 PLT-22 Transceiver Dimensions

Note: If a socket is required for prototype purposes, a Mill-Max #317-93-121-41-005 connector may be used. For more information, contact:

Mill-Max Manufacturing Corporation 190 Pine Hollow Road

Oyster Bay, New York, 11771 Telephone: +1-516-922-6000

Fax: +1-516-922-9253

Internet: http://www.mill-max.com

#### **PLT-22 Transceiver Pinout**

Table 2.1 lists the functions of the PLT-22 transceiver pins.

Table 2.1 PLT-22 Transceiver Pinout

| Pin # | Pin Name       | Function                                                                               |

|-------|----------------|----------------------------------------------------------------------------------------|

| 1     | RXCOMP         | Connection to receive compensation component                                           |

| 2     | RXIN           | Receive signal input from line coupling circuit                                        |

| 3     | GND            | Ground                                                                                 |

| 4     | CP4            | Frame clock synchronization from Neuron Chip (FCLK)                                    |

| 5     | CP2            | Bit clock synchronization from Neuron Chip (BCLK)                                      |

| 6     | CP1            | Transmit data and configuration from Neuron Chip (TXD)                                 |

| 7     | CP0            | Receive data and status to Neuron Chip (RXD)                                           |

| 8     | GND            | Ground                                                                                 |

| 9     | $V_{DD5}$      | +5VDC power supply input                                                               |

| 10    | CKOUT          | Buffered CMOS clock output: 6.5536 MHz ÷ 1, 2, 4 or 8                                  |

| 11    | CKSEL0         | Selects frequency of CKOUT—see table 2.4                                               |

| 12    | CKSEL1/TXON    | Selects frequency of CKOUT—see table 2.4 / TXON (supports PLA-21 Power Line Amplifier) |

| 13    | ~RESET         | Reset input from Neuron Chip                                                           |

| 14    | BIU            | CENELEC Band-In-Use indication output                                                  |

| 15    | PKD            | Packet detect indication output                                                        |

| 16    | TXOUT          | Transmit signal output to line coupling circuit                                        |

| 17    | GND            | Ground                                                                                 |

| 18    | XIN            | 6.5536 MHz oscillator input                                                            |

| 19    | XOUT           | 6.5536 MHz oscillator output                                                           |

| 20    | V <sub>A</sub> | Analog power supply input                                                              |

| 21    | TXLVL          | Transmit level selection input                                                         |

#### **PLT-22 Transceiver Electrical Specifications**

Table 2.2 lists the electrical specifications of the PLT-22 transceiver when used in the CENELEC A-band. All specifications apply over the full operating temperature and supply voltage ranges unless otherwise indicated.

Table 2.2 PLT-22 Transceiver Electrical Specifications

| Parameter                                                                     | Min  | Тур  | Max  | Units     |

|-------------------------------------------------------------------------------|------|------|------|-----------|

|                                                                               |      |      |      |           |

| Operating temperature range <sup>1</sup>                                      | -40  |      | +85  | ° C       |

| V <sub>DD5</sub> input supply voltage                                         | 4.75 | 5    | 5.25 | Volts     |

| V <sub>A</sub> input supply voltage                                           |      |      |      |           |

| TXLVL = GND <sup>2</sup>                                                      | 11.4 | 12.0 | 16   | Volts     |

| I <sub>DD5</sub> input supply current (not including PKD and BIU LED Current) |      |      |      |           |

| receive                                                                       |      | 14   | 20   | mA        |

| transmit                                                                      |      | 13   | 18   | mA        |

| I <sub>A</sub> input supply current                                           |      |      |      |           |

| receive                                                                       |      | 4    | 6    | mA        |

| transmit                                                                      |      | 130  | 200  | mA        |

| TXOUT signal level: TXLVL=GND, into 50• load                                  |      | 6.8  | 7.5  | Volts p-p |

| Output current limit                                                          |      | 1.0  |      | Amps p-p  |

| Output impedance, in-band (transmit)                                          |      | 0.9  | 1.1  | Ohms      |

| Input impedance, in-band (receive)                                            | 500  |      |      | Ohms      |

| PKD output source current @ V <sub>DD5</sub> -0.6 V                           | 8    |      |      | mA        |

| BIU output source current @ V <sub>DD5</sub> -0.6 V                           | 8    |      |      | mA        |

| Power management, lower threshold                                             | 7.2  | 7.9  | 8.5  | Volts     |

| Power management, upper threshold                                             | 11.1 | 12.0 | 12.9 | Volts     |

#### Notes:

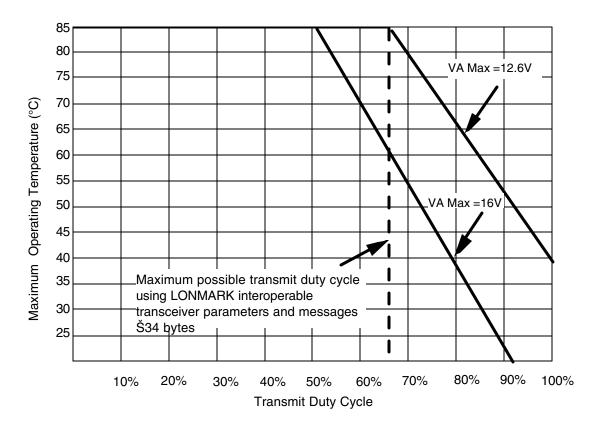

- 1. Maximum operating temperature is a function of  $V_A$  supply voltage and the maximum transmission duty cycle for the node. A maximum operating temperature of 85°C is specified for a  $V_A$  supply  $\leq 12.6 V$  and a maximum transmit duty cycle of 65%, which is the maximum achievable with LONMARK interoperable transceiver parameters and messages of  $\leq 34$  Bytes. For other cases see figure 2.2.

- 2. The  $V_A$  supply must not drop below 11.4V under conditions of typical line voltage, room temperature, and typical current drain (including the PLT-22 transceiver's typical  $I_A$  transmit current of 130mA). This condition ensures adequate transmit amplifier

headroom to drive the full 7Vp-p signal onto typical lines. Under worst case conditions, the minimum  $V_A$  supply voltage may be relaxed **if** the following additional condition is met. With worst case power supply loading (including PLT-22  $I_A$  = 200mA), worst case component tolerances, worst case line voltage, and worst case temperature,  $V_A$  must remain greater than or equal to 9.0V. This condition ensures adequate transmit amplifier headroom when driving low impedance power lines.

When using an energy storage type power supply refer to Chapter 5 for additional timing requirements on the above conditions.

Figure 2.2 PLT-22 Transceiver Maximum Operating Temperature vs. Transmit Duty Cycle

#### **External Components**

#### Crystal

The PLT-22 transceiver requires the connection of an external  $6.5536 \mathrm{MHz}$  crystal for Aband operation. The crystal connects directly to two pins of the PLT-22 transceiver, with no other oscillator components being required external to the transceiver. The crystal should be mounted as close as possible to the transceiver to minimize parasitic effects. The traces connecting the crystal to the transceiver preferably should be less than  $10 \mathrm{mm}$  (0.4") in length, and under no circumstances can they exceed  $20 \mathrm{mm}$  (0.8") in length.

In addition to the nominal frequency specification of 6.5536 MHz, the crystal should be a parallel resonant type with a load rating of 16 pF (series resonant crystals should **not** be used). The frequency accuracy of the oscillator must be held to  $\pm 200$  ppm over the full temperature range of operation.

While the PLT-22 transceiver design is centered around the use of a crystal whose load capacitance rating is 16pF, it is possible to recenter the design for a crystal whose load capacitance rating is higher than 16pF. The PLT-22 transceiver effectively contains two 32pF capacitors, one from XIN to ground and one from XOUT to ground. Note that the *series* combination of the two capacitors equals the load capacitance of the recommended crystal. Recentering the design for the use of a crystal with a higher load capacitance specification requires the addition of two external capacitors whose series equivalent capacitance is equal to the load capacitance specification of the crystal less 16pF. For instance, to use a crystal with a load capacitance specification of 20pF, the operating frequency can be centered by adding two 8.2pF capacitors, one from XIN to ground and one from XOUT to ground.

If a 6.5536MHz±200ppm 0-5V clock signal is already available as part of the node hardware then it may be used as a clock source for the PLT-22 transceiver by connecting it to Pin 18 (XIN) of the transceiver. In this instance Pin 19 (XOUT) of the PLT-22 should be left unconnected. With this option, appropriate high speed clock distribution techniques must be strictly followed in order to ensure that a clean clock signal is present at the XIN pin of the PLT-22 transceiver.

Oscillator frequency accuracy should be checked during the design verification phase of every PLT-22 based product. Frequency accuracy should be measured by using a frequency counter connected to the CKOUT pin to compare the frequency of that pin to 6.5536MHz divided by 8. Be sure that no instruments or extra cabling are connected to either the XIN or XOUT pins of the PLT-22 since even 2pF of extra load on either pin will significantly change the oscillator frequency.

#### Power Supply Bypassing and Grounding

The PLT-22 transceiver requires the connection of external bypass capacitors. The bypass capacitors should be placed as close as possible to the PLT-22 transceiver, and low-impedance ground and supply traces should be used between the PLT-22 transceiver and the bypass capacitors. In addition to the bypass capacitors specified for the Neuron

Chip (see *Neuron Chip Data Book*  $^{2,3,16}$ ), the recommended values of the  $V_{DD5}$  and  $V_{A}$  bypass capacitors are, as follows:

$V_{DD5}$ :

None required if the  $V_{DD5}$  supply at the PLT-22 transceiver pin 9 meets the noise masks described in Chapter 5. It is recommended that PCB designs initially incorporate a  $10\mu F$  10V tantalum capacitor and a  $0.1\mu F$  ceramic capacitor on the  $V_{DD5}$  suppy. These capacitors can be eliminated if the design meets the noise masks in Chapter 5 and passes the receive performance tests described in Chapter 7 without the capacitors installed.

$V_A$ :

$120\mu F$  (minimum) 16V, low-ESR (<0.3 $\Omega$ @ 100kHz), high-frequency aluminum electrolytic capacitor. Low ESR is required in order to minimize  $V_A$  ripple voltage when the transceiver drives low impedance loads, drawing several hundred milli-Amperes of peak-to-peak ripple current. Note that the  $V_A$  bypass capacitor is an integral part of the mains surge protection circuitry described in Chapter 4. In particular, the coupling circuits of Chapter 4 require the use of an aluminum electrolytic type capacitor with a voltage rating of 16V. Higher or lower voltage ratings will likely result in surge immunity which is significantly below the verified levels documented in Chapter 4.

The PLT-22 transceiver provides three ground pins. For proper operation, all three pins must be connected to ground with low-impedance traces, or to a ground plane between the transceiver and the Neuron Chip.

#### Band-In-Use (BIU) and Packet Detect (PKD) LED Connections

The PLT-22 transceiver supplies two output signals, PKD and BIU, that are intended to drive low-current light-emitting diodes (LEDs). Both signals are active-high and must be connected to separate LEDs, with series current-limiting resistors added between the LEDs and ground.

The Band-In-Use function is defined for purposes in the CENELEC C-band and is not required for A-Band operation. When the PLT-22 transceiver is programmed with proper A-band transceiver parameters, as described in Chapter 3, an active BIU signal does not prevent the PLT-22 transceiver from transmitting. Nevertheless, the BIU signal can still be used to indicate when there is a signal in the transceiver's primary carrier frequency range of approximately  $85dB\mu V$  or larger.

The PKD signal is active whenever a valid LonTalk packet is being received by the PLT-22 transceiver. The receive sensitivity of the transceiver is considerably greater than that of the BIU indicator. The PKD signal will go active when the PLT-22 transceiver receives packets whose signal level is as small as  $40dB\mu Vrms$ . Thus it is not uncommon for the PKD indicator to signal that a packet is present without the BIU indicator turning on; this occurs in cases where the received packet signal strength is less than the BIU threshold.

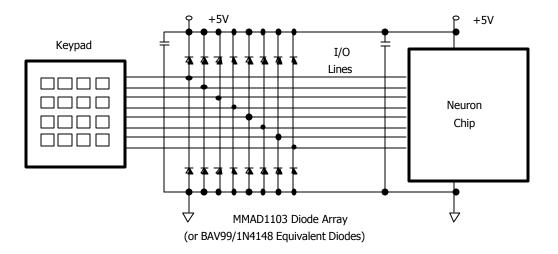

Both the BIU and PKD signals are driven directly by the PLT-22 transceiver's DSP processor. ESD protection diodes should be connected to these pins in applications where the BIU and PKD signals drive LEDs that could be subject to ESD exceeding 2kV. In applications where the LEDs are surrounded by a metallic ground plane, such

as a hole in a grounded metal enclosure, the ESD diodes may not be necessary. However, if a plastic or metal enclosure without a good ground connection is used, then ESD diodes are needed to prevent damage to the PLT-22 transceiver. ESD protection diodes include industry part types 1N4148 (thru-hole) and BAV99 (SMT).

#### **Neuron Chip Connections**

The link between the Neuron Chip and the PLT-22 transceiver makes use of the Neuron Chip's special-purpose mode interface. This interface requires that the CP and ~RESET lines of the two devices be interconnected as shown in table 2.3.

| Neuron Chip Pin | PLT-22 Pin     |

|-----------------|----------------|

| CP0             | 7              |

| CP1             | 6              |

| CP2             | 5              |

| CP3             | Do not connect |

4

13

10

CP4

~Reset

CLK1

Table 2.3 Neuron Chip and PLT-22 Transceiver Interconnections

The Neuron Chip and PLT-22 transceiver should be placed adjacent to one another on the same printed circuit board. The length of the  $\sim$ RESET and CP lines should be kept to an absolute minimum and in no case should exceed 50mm (2"). In addition, the ground traces and  $V_{DD5}$  trace between the PLT-22 transceiver and the Neuron Chip should have impedances as low as possible.

When the PLT-22 transceiver is operated in the A-band (with a 6.5536MHz crystal), a second and separate crystal is required to operate the Neuron Chip at one of its standard operating frequencies of 2.5MHz, 5MHz, or 10MHz. Note that the minimum Neuron Chip clock frequency required for use with the PLT-22 transceiver operating in the A-band is 2.5MHz.

For A-band operation the CKOUT pin of the PLT-22 transceiver should be left unconnected. The CKSEL1 pin of the transceiver should be left open, unless it is used to drive the TXON pin of a PLA-21 Power Line Amplifier. The CKSEL1/TXON pin must never be connected directly to a supply rail. The CKSEL1/TXON pin will draw large currents and potentially damage the PLT-22 transceiver if it is connected directly to a supply rail. The CKSEL0 pin of the transceiver should be connected to ground and should not be left open.

The PLT-22 transceiver ~RESET pin is designed to connect directly to the Neuron Chip ~RESET pin. The *Neuron Chip Data Book* <sup>2,3,16</sup> provides information on the Neuron Chip's external reset circuitry. **Depending on the particular Neuron Chip** version used, a Low Voltage Indicator (LVI) circuit such as the Motorola

MC33064 or Dallas 1233 may be necessary to supply a reset signal to both the Neuron Chip and the PLT-22 transceiver. All of the application circuits shown in this documentation include an LVI chip. Consult your Neuron Chip manufacturer for the latest reset circuit requirements. Whether an LVI chip or a simpler discrete circuit is required, the ~RESET pin of the PLT-22 should always be tied directly to the ~RESET pin of the Neuron Chip. To minimize the effect of ESD discharges on the Neuron Chip ~RESET pin, use two external 56pF ceramic capacitors, one tied between ~RESET and  $V_{DD5}$ , the other between ~RESET and GND. The capacitors should be placed as close as possible to the Neuron Chip ~RESET pin. Note that the PLT-22 transceiver already incorporates two 56pF capacitors on the ~RESET line internal to the transceiver. These internal capacitors should be taken into account when calculating the total allowable capacitive load on the Neuron Chip ~RESET pin, as specified in the Neuron Chip Data Book<sup>2,3,16</sup>.

#### **Transmit Output Level**

The TXLVL input pin on the PLT-22 transceiver determines the output voltage of the transmit signal. For A-band operation of the PLT-22 transceiver, the TXLVL pin should be grounded so that the transceiver will transmit a 7Vp-p signal. This level satisfies CENELEC 50065-1 signal level requirements for operation in the A-band. Since the 20dB bandwidth of the PLT-22 A-band signal is >5kHz, CENELEC regulations require that the overall signal level not exceed 134dB $\mu$ V and that the spectrum of the signal not exceed 120dB $\mu$ V within a 200 Hz bandwidth. When used with a recommended coupling circuit from Chapter 4, the overall level of the PLT-22 transceiver operated at 7Vp-p is 121dB $\mu$ V and its level with a 200 Hz bandwidth filter is 117dB $\mu$ V.

#### **TXON Output Signal**

The PLT-22 transceiver provides an output signal suitable for controlling a PLA-21 Power Line Amplifier via the CKSEL1/TXON pin. The CKSEL1/TXON pin functions as an input during the period in which the ~RESET pin of the PLT-22 transceiver is held active (low). After RESET becomes inactive (high) CKSEL1/TXON changes to an output (CKSEL0 remains an input, but its state is ignored). The output, called TXON, is a buffered version of the internal signal used to control the transceiver's output amplifier. The TXON signal output is active high when the PLT-22 transceiver transmits packets.

The TXON signal is typically used to provide tri-state control of an external booster amplifier, such as the PLA-21 Power Line Amplifier model 53001-01. For more details see the *PLA-21 Power Line Amplifier Specification and User's Guide*.

2-10

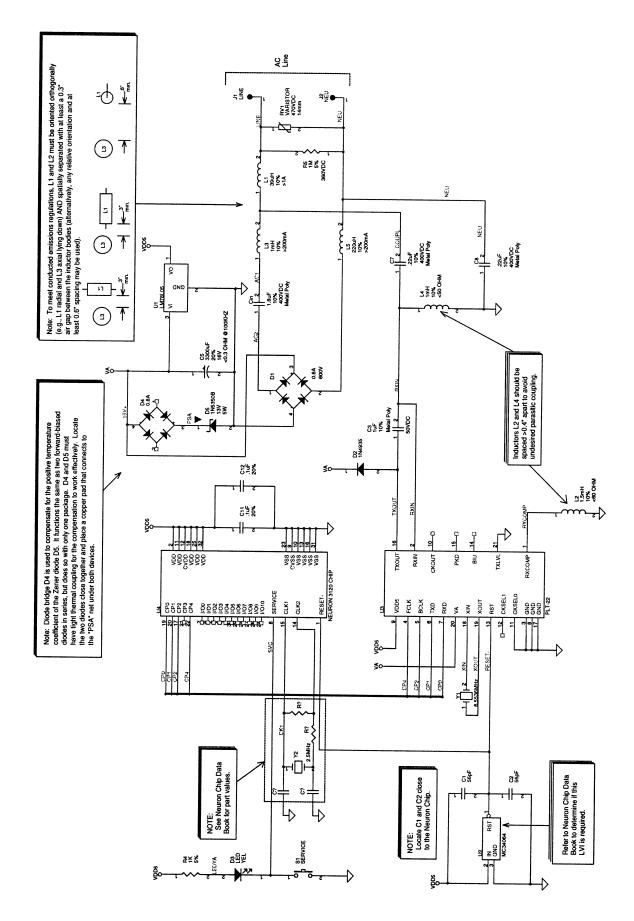

Figure 2.3 Neuron 3120 Chip Application Schematic

## **PLT-22 Transceiver Programming**

Certain parameters of the PLT-22 transceiver are programmed by the user. This chapter presents a list of these parameters and their values, plus a description of how they are programmed via the LonBuilder Developer's Workbench and the NodeBuilder Development Tool.

#### **Dual Carrier Frequency Mode**

Each PLT-22 transceiver incorporates a new dual carrier frequency capability which allows it to communicate with other PLT-22-based nodes, even if noise is blocking its primary communication frequency range. If impairments prevent communication in this range, a PLT-22-based node can automatically switch to a secondary carrier frequency to complete a transaction with other PLT-22-based nodes.

With dual carrier frequency mode, the last two retries of acknowledged service messages are sent using the secondary carrier frequency. Thus when acknowledged service is used with three retries (four total tries), the first two tries are sent using the 86kHz primary carrier frequency. If the last two tries are needed to complete the transaction, they are sent (and acknowledged) using the 75kHz secondary carrier frequency. A minimum of two retries must be used if the PLT-22 transceiver is to be able to use both carrier frequency choices. For optimum reliability and efficiency, Echelon recommends the use of three retries when using acknowledged service messaging with the PLT-22 transceiver.

When unacknowledged repeat message service is used, the PLT-22 transceiver leverages the reliability of both carrier frequencies by alternating between them. In this case an unacknowledged repeat message with three repeats results in the first and third packets being sent using the 86kHz primary carrier frequency, while the second and fourth packets are sent using the 75kHz secondary carrier frequency. A minimum of one repeat must be used for the PLT-22 transceiver to use both carrier frequency choices. For improved reliability, three repeats are recommended.

#### **CENELEC Access Protocol**

CENELEC regulations do not specify an access protocol for use in the CENELEC A-band. When programmed with the A-band transceiver parameters described later in this chapter, the PLT-22 transceiver's internal CENELEC access protocol is disabled. With this selection, an active Band-In-Use signal will <u>not</u> prevent a PLT-22 from transmitting.

#### **Power Management**

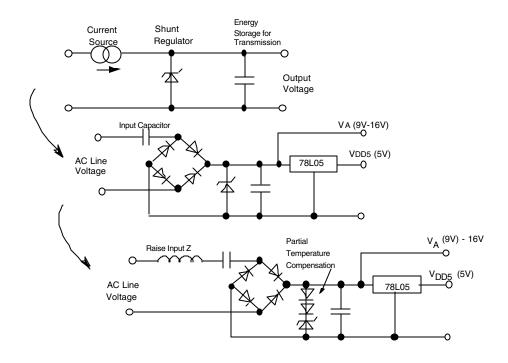

The PLT-22 transceiver incorporates a power management feature that supports the design of very low cost power supplies in low cost consumer applications. This class of consumer applications generally has low transmit duty cycle operation requirements. These low cost power supplies take advantage of a number of PLT-22 features: the low receive current requirements of the PLT-22 transceiver; the 9:1 difference between the PLT-22 transceiver transmit and receive mode currents and the wide  $V_{\rm A}$  operating voltage of the PLT-22 transceiver.

A low transmit duty cycle implies that the device transmits packets infrequently, e.g., the product waits for a minimum of 10 packet times between transmitting each packet - a 10% transmit duty cycle. A power supply design that takes advantage of this duty cycle can store energy on a capacitor during the relatively long period between transmissions, when the PLT-22 transceiver draws minimal current, and then consume the stored energy to transmit a packet. This type of power supply, referred to as an

"energy storage power supply," stores energy by charging an energy storage capacitor to a relatively high voltage (e.g., 15V) while in receive mode. The voltage on the capacitor then falls or "droops" toward a lower limit (e.g., 9.0V) while transmitting. The energy storage capacitor is then slowly recharged to the higher voltage during the relatively long time between transmissions. Traditionally, the proper design of such a power supply required knowledge of the maximum transmit duty cycle to be supported, and an implementation that accounted for all worst case operating conditions (temperature, line voltage, component variation and transmitter loading).

The cost of such a power supply can be significantly reduced if, instead of designing the supply for the maximum possible transmit duty cycle and for the worst case environmental conditions, the supply can be designed for typical operating conditions. However, designing for typical operating conditions implies that a mechanism exists to "manage" the worst case operating conditions such that reliable operation is assured. This management feature must also address products whose operating conditions (especially transmit duty cycle) are not defined prior to use in a network, but rather are controlled by application programs loaded after installation.

The PLT-22 power management feature implements the needed management functionality by intelligently monitoring the energy storage power supply. Should the node attempt to transmit too frequently, the power management feature enforces a limit on the transmit duty cycle by preventing the Neuron Chip from transmitting until the node's power supply recovers to the point that sufficient energy is available to transmit a packet. Details of this feature and application examples are provided in Chapter 5.

When power management is enabled, the PLT-22 transceiver requires a  $V_A$  power supply voltage of 12.9V before it will attempt to transmit a packet. Products with fixed  $V_A$  power supplies lower than 12.9V should <u>never</u> be programmed to enable the power management feature as they may never be allowed to transmit. Likewise a node whose power supply relies on power management to operate correctly should <u>never</u> be programmed with the power management feature disabled.

The user can enable or disable power management at the time of channel definition by selecting a standard transceiver type with a "low" suffix. The only difference between a set of standard transceiver parameters with the "low" suffix and the corresponding set without the "low" suffix is that the power management feature is enabled with the "low" set and disabled with the set without the suffix.

Note that some installation tools load a device's communication parameters as part of the installation and replacement process and calculate those parameters based on the channel (rather than the particular device). Such tools can not be used for systems that contain a mixture of nodes with and without power management enabled on the same channel.

Tools based on the LONWORKS Network Services (LNS) architecture, such as LonMaker for Windows Integration Tool, correctly support all configurations of PLT-22 nodes with or without power management. For a tool not based on LNS, contact your tool vendor to determine if it can support a mixture of power management and non-power management nodes on the same channel.

#### **Standard Transceiver Types**

Two standard transceiver types are defined for the PLT-22 transceiver operating in the A-band. These standard transceiver types specify communications parameters for a PLT-22 node. The communication parameters of the two standard types are identical except for the state of the power management feature (enabled or disabled) of the PLT-22 node.

Table 3.1 lists the names of the two standard transceiver types and shows the difference between them.

Table 3.1 Standard PLT-22 Transceiver Types

| Standard Transceiver Type | Power Management |  |

|---------------------------|------------------|--|

| PL-20A                    | Disabled         |  |

| PL-20A-LOW                | Enabled          |  |

Table 3.2 shows which standard transceiver types are allowed versus power supply types.

Table 3.2 Allowed Power Supply Types Versus Standard Transceiver Types

| Standard Transceiver<br>Type Selection | Fixed V <sub>A</sub> power supply <12.9V | Energy Storage V <sub>A</sub> power supply >12.9V                                                               |

|----------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| PL-20A                                 | ОК                                       | Not allowed if the power supply design relies on power management for worst case duty cycle and load conditions |

| PL-20A-LOW                             | Not allowed: node may not transmit       | ОК                                                                                                              |

# LonBuilder and NodeBuilder PLT-22 Transceiver Channel Definitions

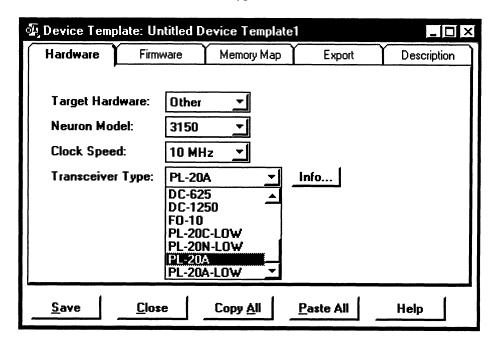

To use the PLT-22 transceiver in the CENELEC A-band with the LonBuilder or NodeBuilder tools, you must have STDXCVR.TYP file with a date stamp of 1999 or later. STDXCVR.TYP files earlier than 1999 do not include either of the PL-20A types. Verify that the year on the date of your STDXCVR.TYP file is 1999 or later by locating it in the LONWORKS TYPES directory (c:\lonworks\types by default) for the NodeBuilder software, and in the LonBuilder TYPES directory (c:\lb\types by default) for the LonBuilder software. If the date on your STDXCVR.TYP file is older than 1999, you can download an update from Echelon's web site at www.echelon.com/toolbox.

Once you have verified that you are using the correct version of the STDXCVR.TYP file, specify PL-20A or PL-20A-LOW as the standard transceiver type in the NodeBuilder

Device Template, as shown in figure 3.1, or the LonBuilder Channel Create window. Select "Yes" for the "Enforce Standard Type" field.

Figure 3.1 NodeBuilder Device Template Window

Table 3.3 shows the channel definition parameters for the PLT-22 transceiver. If you do not have access to an updated STDXCVR.TYP file, these channel definition parameters may be entered in the Channel Modify screen and sub-screens to create a standard PLT-22 transceiver definition equivalent to the PL-20A or PL-20A-LOW parameters

**Table 3.3** Channel Definition Parameters for the PLT-22 Transceiver

| Parameter             | Value           |

|-----------------------|-----------------|

| Channel Modify Screen |                 |

| Std Xcvr Type         | Custom          |

| Comm Mode             | Special Purpose |

| Comm Rate             | 1.25Mbps        |

| Number of Priorities  | 8               |

| Min Clock Rate        | 2.5MHz          |

| Avg Pkt Size          | 15 bytes        |

| Osc Accuracy          | 200ppm          |

| Osc Wakeup            | 0 µsec          |

Table 3.3 Channel Definition Parameters for the PLT-22 Transceiver (continued)

| Comm Mode Specific Parameters                    |                      |

|--------------------------------------------------|----------------------|

| Channel Bit Rate                                 | 2613 bps             |

| Alternate Bit Rate                               | 2613 bps             |

| Wakeup Pin Dir                                   | Output               |

| Xcvr Controls Preamble?                          | Yes                  |

| General Purpose Data (power management disabled) | 0E 01 00 10 00 00 00 |

| General Purpose Data (power management enabled)  | 0E 01 00 12 00 00 00 |

| Allow Node Override?                             |                      |

| PL-20A, PL-20A-LOW                               | YES                  |

| Layer 1 Time Factors                             |                      |

| Rcv Start Delay                                  | 6.8 bits             |

| Rcv End Delay                                    | 1.6 bits             |

| Indeterm Time                                    | 0.0 bits             |

| Min Interpacket                                  | 17.5 bits            |

| Preamble Len                                     | 33.5 bits            |

| Use Raw Data?                                    | No                   |

The standard transceiver definitions in table 3.1 were chosen as the best balance between flexibility in network design and network throughput. Flexibility is provided by the selection of 8 priority slots on the channel and a minimum input clock of 2.5MHz (a Neuron Chip input clock frequency as low as 2.5MHz may be chosen in order to reduce node power consumption). These parameters support a packet rate of 6 packets/sec with 80% throughput, 4% collisions, and 11 byte packets.

4

# **Coupling Circuits**

This chapter includes a technical discussion about the means by which communication signals are coupled to power mains. Coupling circuit designs, including schematics and electrical safety issues, are included.

#### **Power Line Communications**

The PLT-22 transceiver employs sophisticated digital signal processing techniques, a transmit power amplifier with a very low output impedance, and a very wide (>70dB) dynamic range receiver to overcome the signal attenuation and noise inherent in power mains communication. Maintaining the full communication capability of the PLT-22 transceiver requires careful selection and implementation of the mains coupling circuitry external to the PLT-22 transceiver. This section gives an overview of the sources of signal attenuation as a basis for understanding choices in selecting and implementing mains coupling circuits.

Attenuation is the difference between the signal level at the output of the power line transmitter and the level of that same signal at the input of the intended receiver. While attenuation is technically defined as the ratio of power levels, it is referred to in this document as the ratio of the transmitted signal voltage (unloaded) to the voltage of that same signal at the receiver input. A voltage ratio is more convenient to measure since power measurements require knowledge of the circuit impedance which, in the case of the power mains, varies with both location and time.

In power mains communications the attenuation of transmitted signals spans a wide range and is most conveniently denoted in decibels (dB), where voltage attenuation is defined in dB as  $20\log_{10}$  (V<sub>transmit</sub>/V<sub>receive</sub>). Thus 20dB of attenuation means that the signal was reduced by a factor of 10 by the time it arrived at the receiver, 40dB of attenuation corresponds to a factor of 100, 60dB a factor of 1000, and so on. A PLT-22 transceiver operating in the A-band is capable of reliably communicating on a low-noise line when the transmit signal is attenuated by as much as 77dB (a factor of 7,000). Thus a signal transmitted at 7Vp-p (2.5Vrms) may be received when reduced to less than 1mVp-p ( $350\mu\text{Vrms}$ ).

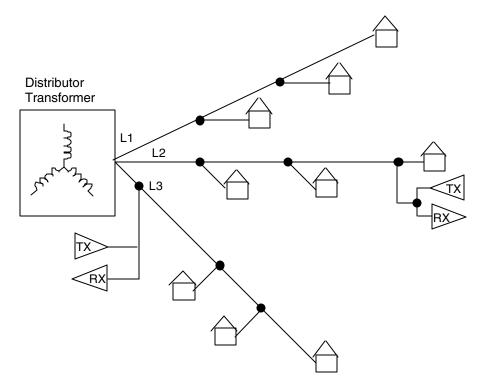

To better understand the sources of attenuation in a power mains network, it is helpful to look at a simplified model of a power distribution network. This example is based on an installation having one power distribution transformer and three phases of mains power. While many applications for power line communication employ different topologies, this example illustrates some of the key issues affecting the successful application of the PLT-22 transceiver.

Figure 4.1 depicts the path that a power line communication signal might traverse, starting from a utility distribution transformer and passing through the distribution wiring to the electricity meter on a particular home. Each home in the power network may power devices that generate noise and load the transmitted signal.

Figure 4.1 Power Distribution Model

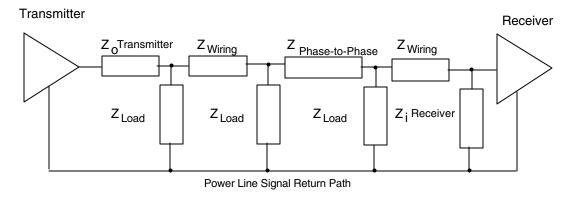

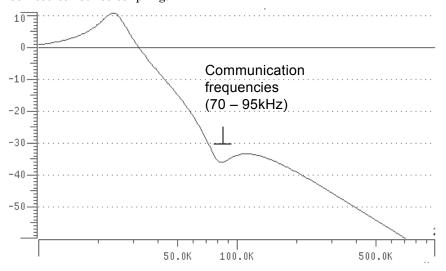

Attenuation is most easily understood in terms of a voltage-divider circuit formed by the output impedance of the transmitter, the impedance of the various mains distribution branches, and any loads present. At A-band communication frequencies of the PLT-22 transceiver (70kHz to 95kHz), the significant impedances are due to the series inductance of the mains wiring itself, and capacitive and resistive loads between line and neutral. Another source of attenuation occurs in the example of figure 4.1 when the communicating devices are not all connected to the same AC mains phase. Mutual inductance and parasitic capacitance provide partial (but imperfect) coupling between circuit phases. If these distributed impedances are lumped together and treated as if a single frequency is being transmitted, the simple model shown in figure 4.2 results.

Figure 4.2 Power Mains Attenuation Model

This model illustrates that minimizing the series impedances and maximizing the line-toreturn path impedances reduces the attenuation of the transmitted signal.

#### **Coupling Techniques**

#### Power Line Coupling Basics

PL Transmitter

Injecting a communication signal into a power mains circuit is normally accomplished by capacitively coupling a transceiver's output to the power mains. In addition to the coupling capacitor, an inductor or transformer is generally present. The coupling capacitor and the inductor or transformer together act as a high-pass filter when receiving the communications signal. The high-pass filter attenuates the large AC mains signal (at 50Hz), while passing the transceiver's communication signal. Figure 4.3 below shows a basic mains coupling circuit. The value of the capacitor is chosen to be large enough so that its impedance at the communication frequencies is low, yet small enough that its impedance at the mains power frequency (50Hz) is high. The impedance of the capacitor can be considered as part of the transmitter's output impedance ( $Z_{\rm OTransmitter}$ ) shown in figure 4.2. Keeping the impedance of the coupling capacitor low minimizes the signal injection loss caused by the voltage divider formed between the output impedance of the amplifier and the mains loading ( $Z_{\rm Load}$ ).

The value of the inductor is chosen to have a relatively high impedance at the PLT-22 transceiver's communication frequencies. The inductor impedance can be considered part of the receiver input impedance ( $Z_{i\ Receiver}$ ) shown in figure 4.2. Keeping the inductor impedance high helps minimize any signal loss at the receiver due to the voltage divider formed by the wiring impedance and the receiver input impedance.

# Neutral PL Receiver

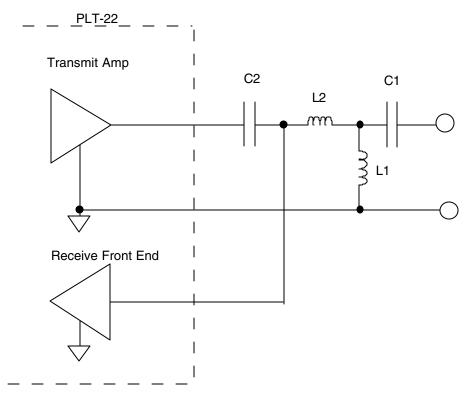

Figure 4.3 Basic Mains Coupling Circuit

In the following section the simple circuit shown in figure 4.3 is expanded to make it practical in real applications. At the end of this chapter, recommended coupling circuit schematics and component specifications are provided.

#### Power Line Coupling Details

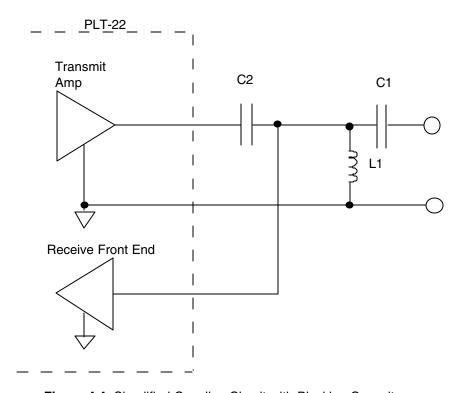

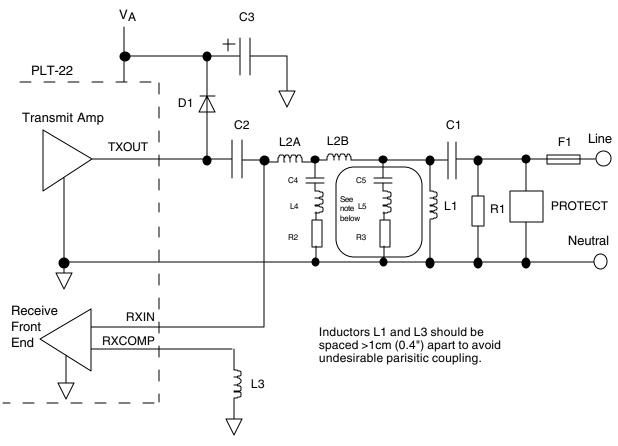

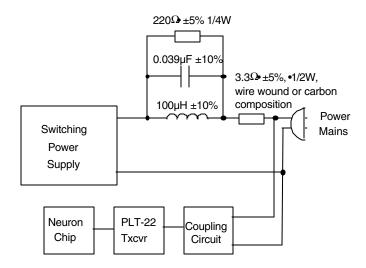

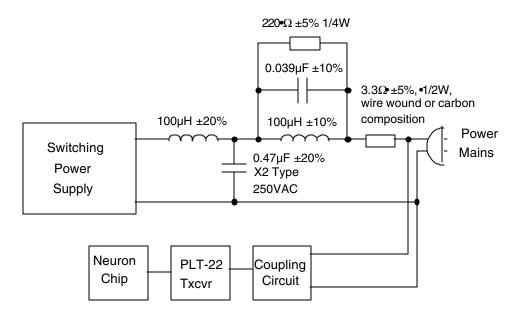

The coupling circuit shown in figures 4.3 requires the addition of a small number of components to make it practical. Figure 4.4 shows the addition of an AC coupling capacitor (C2) to prevent the inductor from shorting the transmit amplifier's DC bias voltage.

Figure 4.4 Simplified Coupling Circuit with Blocking Capacitor

Given the attenuation model presented earlier in figure 4.2, one critical design constraint is that the series combination of C1 and C2 must have a low impedance at the PLT-22 transceiver's communication frequencies. The impedance of these capacitors, along with the PLT-22 transceiver's transmit output impedance, corresponds to " $Z_0$  Transmitter" in figure 4.2. Since the equivalent load impedance of the power line may in some cases be as low as 1-2 Ohms, and since the output impedance of the PLT-22 transceiver is less than 1 Ohm, the impedance of these capacitors should be on the order of 1 Ohm so that they do not add significantly to " $Z_0$  Transmitter". While the values of C1 and C2 could be set high enough to meet this goal, doing so would significantly increase the cost of the high-voltage capacitor C1. Since C2 is connected only to low voltage, and thus is lower cost for a given value, its value can be set higher relative to the value of the high-voltage capacitor C1. A simple, cost-effective solution is obtained when an inexpensive inductor, L2, is added as shown in figure 4.5 below. This inductor forms a series-resonant circuit with C1 and C2,

and its value can therefore be chosen to optimize coupling at the PLT-22 transceiver's communication frequencies while minimizing the cost of C1 and C2.

Figure 4.5 Simplified Coupling Circuit with Resonant Inductor

An important design constraint on L2 is that its DC resistance be kept very low since it is in the transmit signal path and effectively part of the transmitter's output impedance. Low-cost inductors with DC resistance on the order of 0.2 Ohms are widely available.

Capacitors C1 and C2 should be of metalized polyester construction in order to minimize equivalent series resistance and provide adequate surge immunity.

It is critical that no additional series impedance be added in the signal path between the TXOUT pin of the PLT-22 transceiver and the power mains (or in the return path from the power mains to the ground pins of the PLT-22) unless verified to be significantly less than 1 Ohm near 85kHz. If, for example, a ferrite bead with an impedance of 9 Ohms at 85kHz were added then the signal injected into a 1 Ohm power line would be reduced by a factor of 10. Under typical conditions the end product would still function, however, communication margin and reliability over a full range of power line environments would be severely compromised. For the same reason, the impedance of series circuit protection elements must also be kept very low. Low current fuses (<2A), protection devices that can be reset, and ferrite beads generally add unacceptable series impedance to the signal path.

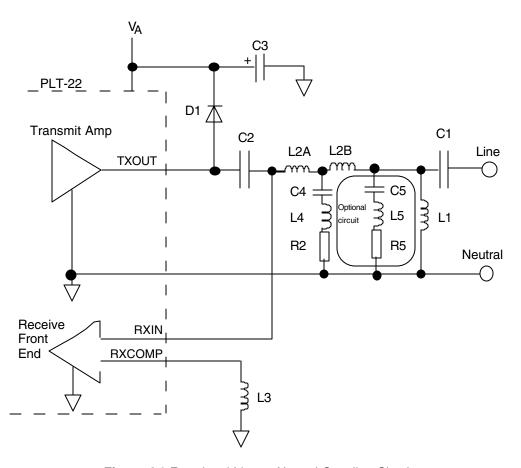

Figure 4.6 shows additions to the coupling circuit, which are required to make it fully functional. The first is a 1.5mH inductor, L3, connected to the PLT-22 transceiver receive filtering circuitry. The DC resistance of L3 can be up to 60 Ohms. The second is the LCR trap circuit consisting of C4, L4, and R2. This circuit is added to attenuate out-of-band spurious emissions and comply with CENELEC conducted emission regulations. The third is a diode, D1, connected from the transmitter to the amplifier supply voltage  $(V_A)$  to protect the inputs of the PLT-22 transceiver from large (>15V) transients. This diode works in conjunction with a diode internal to the PLT-22 transceiver that connects from the transmitter output to ground. Bypass capacitor C3 also has been added to emphasize the fact that it is an integral part of the coupling circuit. One of the functions of this capacitor is to protect the V<sub>A</sub> supply line from excessive overshoot when positive going line surges discharge through diode D1. The last addition is an optional circuit that improves performance in environments where large (>20V) impulses may be present from devices such as SCRcontrolled loads. This circuit consists of an LCR series network that acts as a notch filter whose center frequency is at the characteristic "ringing" frequency of the coupling circuit. This optional circuit should be included on nodes which will be operated in environments where large (>20V) implusive noise is expected on each ac mains half cycle (i.e., at a 100 Hz rate).

Figure 4.6 Functional Line-to-Neutral Coupling Circuit

In instances where large ambient fields may be present (such as from switched mode power supply open frame magnetic elements), it is possible that one or more of the PLT-22 coupling circuit inductors may pick up these stray fields and conduct them onto the power mains. Depending on the frequency and amplitude of these fields they could result in failure to meet CENELEC conducted emission regulations.

If noise from parasitic coupling is suspected, it can be confirmed by inserting a 10cm (4") twisted wire pair in series with one of the inductors in question. If the conducted noise spectrum varies by more than a few dB when this inductor is moved closer to, and farther from, other components, then parasitic coupling may be the source of the problem.

If stray coupling is a problem, regulations can usually be met by adjusting the location or orientation of the radiating device relative to the coupling circuit inductors. Alternately, shielded or toroidal inductors may be used to reduce coupling as long as all electrical parameters specified in the example coupling circuit tables given later in this chapter are met. If, however, a toroidal or shielded inductor is used in place of L2A or L2B, then the selected part must handle the maximum 1App output current of the PLT-22 transceiver without approaching saturation. If either L2A or L2B even approaches saturation they can add harmonics of the PLT-22 transmit signal which may result in failure to meet CENELEC emission regulations (in this instance, due to inductor distortion instead of a stray pickup). For this reason, a shielded or toroidal inductor used for L2A or L2B may need to have DC current rating two or three times higher than listed in the example circuits given later in this chapter. Note that the recommended open frame axial inductors do not need this extra operating margin due to the linearity provided by its magnetic path being partly in air.

#### Safety Issues

This guide is intended only as an introduction to some of the safety issues associated with designing circuits using the PLT-22 transceiver. This document is not a primer on electrical safety or electrical codes, and it is the responsibility of the user to familiarize himself or herself with any applicable safety rules or regulations. A review of all designs by competent safety consultants and the pertinent regulatory or safety agencies is strongly recommended.

# Safety Isolation Considerations

Many products include an isolation barrier in the form of an insulated enclosure between a user and any hazardous conductors. A typical product of this type is a light switch in which the PLT-22 transceiver and all of the associated electrical components are contained inside the switch enclosure. The type of coupling circuit that can be used in these applications is called a *non-isolated coupling circuit*. A non-isolated coupling circuit generally requires lower cost components, making it especially desirable for use in price-sensitive consumer products and wiring devices. All of the coupling circuit examples that have been shown so far are of the non-isolated type.

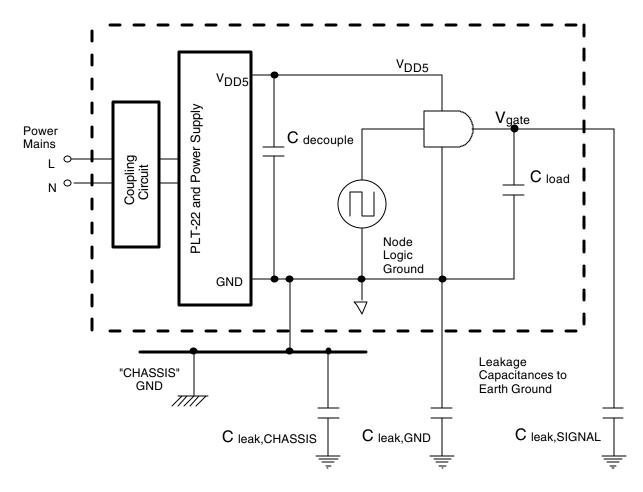

Some products cannot practically incorporate an enclosed isolation barrier and an alternate method of safety isolation must then be provided. For example, a circuit board that uses a PLT-22 transceiver, a non-isolated line-to-neutral coupling circuit, and a Neuron Chip

whose I/O pins are user-accessible presents a potential electrical shock hazard. Since the mains neutral lead is connected directly to the circuit board common, the user could be exposed to a hazardous voltage at the I/O connector, especially if the line and neutral connections are accidentally reversed. Additional circuitry is needed in such a product to provide a safety isolation barrier between the user-accessible I/O connector and the mains line and neutral conductors.

The most common solution is to provide isolation in the coupling circuit by modifying the simple coupling circuit described earlier. This style of coupling circuit is referred to as an *isolated coupling circuit*.

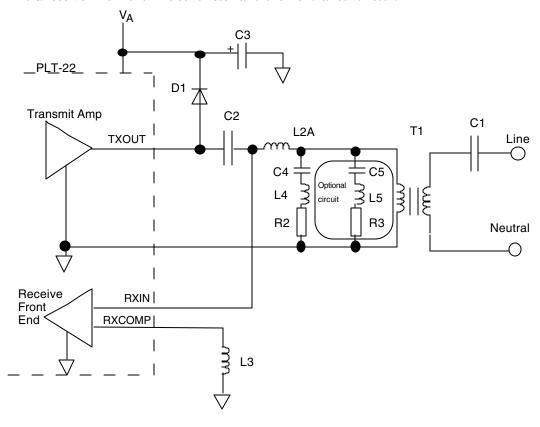

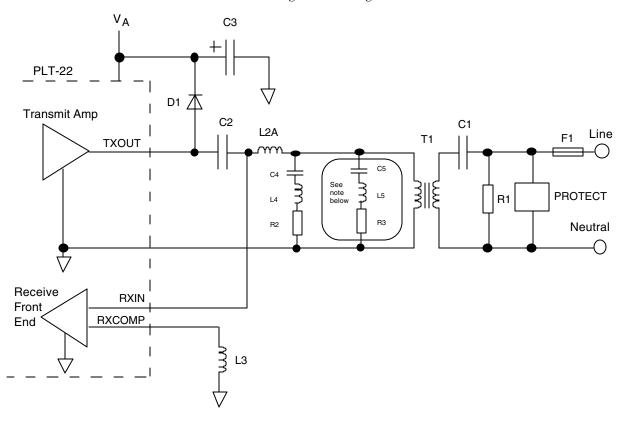

The preferred isolated coupling circuit uses *transformer-isolation*. Transformer-isolation requires substituting a safety agency-approved transformer having the appropriate communication characteristics in place of L1 (see Appendix A). Transformer-isolated coupling has the advantage that the resonant inductor L2B can be incorporated into the isolation transformer by designing the leakage inductance of the transformer to match the value of L2B. A transformer-isolated coupling circuit is shown in figure 4.7, where it can be seen that the transformer isolates the PLT-22 transceiver from the line conductor and the neutral conductor.

Figure 4.7 A-band Transformer-Isolated Coupling Circuit

An alternate method of providing safety isolation is to add optical isolation between the Neuron Chip and the I/O connector, or between the Neuron Chip and the PLT-22 transceiver. If optical isolation is used between the Neuron Chip and the PLT-22

transceiver, then a maximum of 150ns propagation delay may be added to the CP interface lines in either direction.

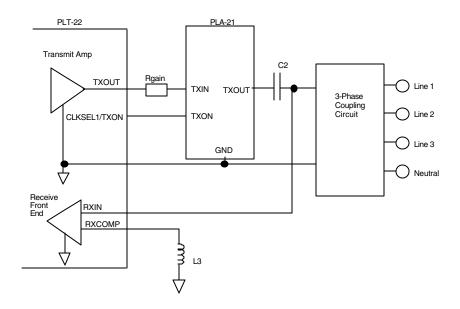

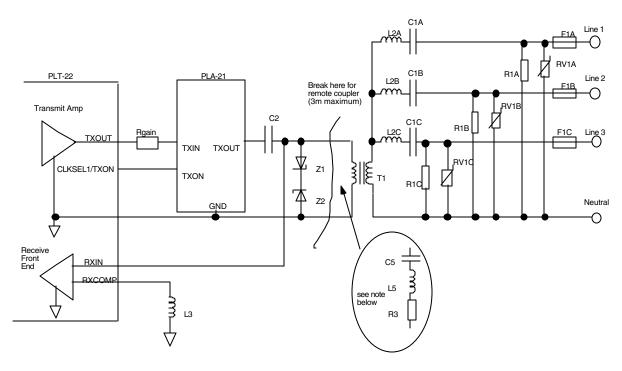

#### 3 Phase AC Mains Circuits

When communicating between PLT-22-based nodes located on different ac power phases, a significant portion of the overall attenuation between nodes is caused by loss in crossing phases (typically 10-20dB). Most of this loss can be avoided if one of the two nodes couples its signals to all three phases. In the example illustrated in figure 4.1 if all communications are to (and from) the node located at the central distribution transformer, then the use of a 3-phase coupling circuit in that node is recommended to maximize communication distance. Due to the fact that this central node must then drive the parallel combination of the impedance from all three phases, the use of a PLA-21 Power Line Amplifier is also recommended in that node to further extend operating distance.

Figure 4.8 illustrates how the PLA-21 Amplifier is connected between a PLT-22 transceiver and 3-phase coupling circuit. Refer to figure 4.12 and table 4.5 for detailed component values.

Figure 4.8 Connecting the PLA-21 Amplifier

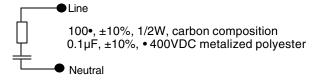

# Capacitor Charge Storage

The coupling capacitors depicted in the earlier figures can retain substantial charge even after a PLT-22 transceiver-based device has been disconnected from the power mains. This can be of significant concern in applications where a line cord could be touched by a user after being disconnected from the power mains. To minimize potential shock hazard, coupling circuits should include a large value bleeder resistor to discharge the capacitors following disconnection from the mains. Even in applications where the connection to the mains is permanently wired, it is good practice to include the resistor to protect service personnel. The coupling circuit schematics in this document include appropriate bleeder resistors.

# Line Surge Protection

Coupling circuits that connect the PLT-22 transceiver to the power mains also require the addition of component(s) to provide protection of the PLT-22 transceiver from the high-voltage surges that occur on all power distribution systems. Primarily lightning induced, these surges can present voltages of 6kV or greater at very high current levels for brief periods to the coupling circuits. The recommendations that follow are based on testing performed on a particular PCB layout. The efficacy of the surge protection implemented in each product containing the PLT-22 transceiver must always be verified empirically, since factors such as PCB layout and packaging can influence the results as much as the choice of protection components.

The level of surge protection required for a given product often depends on the installed location of the product to be protected. Devices connected to branch circuits within a building or home are typically subject to the lowest level of surge stress. Devices connected at, or close to, the power entry point of a building or home, e.g., electrical meters and main breaker panels, are subject to higher levels of surge stress. Devices connected to outdoor wiring are subjected to the highest surge stress of all.

Standard tests for surge immunity are defined in IEEE C62.41-1991<sup>15</sup> and CEI/IEC 1000-4-5<sup>14</sup>. Both documents classify levels of surge stress by the type of surge wave-form (either Ring wave or Combo wave), surge voltage, and surge current. In addition to describing standard test methods, both documents also suggest surge immunity levels for the device environments described above.

Comparison of the two documents reveals that their recommended test procedures are identical, while the suggested immunity levels called out in IEEE C62.41-1991 substantially exceed the suggested immunity levels of CEI/IEC 1000-4-5. The more severe (and thus more conservative) immunity levels called out in IEEE C62.41-1991 were used in characterizing the recommended surge protection circuitry shown in the PLT-22 transceiver coupling circuit examples that follow.

The line-to-neutral coupling circuits documented later in this chapter have been demonstrated to meet the IEEE C62.41-1991 "high system exposure" levels with no damage for *branch circuit applications*, *power entry applications*, and *outdoor wiring applications*, up to the limits of the available test equipment.

Table 4.1 summarizes the surge immunity of the PLT-22 transceiver in conjunction with the specified line-to-neutral coupling circuits.

Table 4.1 Line-to-Neutral Coupling Circuit Surge Immunity Test Results

|                     | Ring Wave Test                               |           | Combo Wave Test                               |                                                 |  |

|---------------------|----------------------------------------------|-----------|-----------------------------------------------|-------------------------------------------------|--|

|                     | (0.5μs-100kHz)                               |           | (1.2/50μs-8/20μs)                             |                                                 |  |

| Product<br>Location | IEEE C62.41-1991<br>system exposure<br>level |           | IEEE C62.41- 1991<br>system exposure<br>level | Surge level<br>verified not to<br>damage PLT-22 |  |

| Branch Circuit      | low -2kV @70A                                |           |                                               |                                                 |  |

|                     | med-4kV @130A                                |           | Not specified                                 | 6kV @500A                                       |  |

|                     | high-6kV @200A                               | 6kV @200A |                                               | 2kV @1,000A                                     |  |

| Power Entry         | low -2kV @170A                               |           | low -2kV @1,000A                              |                                                 |  |

|                     | med-4kV @330A                                |           | med-4kV @2,000A                               |                                                 |  |

|                     | high-6kV @500A                               | 6kV @500A | high-6kV @3,000A                              | 6kV @3,000A                                     |  |

| Outdoor Wiring      | Not specified                                | 6kV @500A | low -6kV @3,000A<br>med-10kV @5,000A          | 6kV @3,000A<br>(limited by test<br>equipment)   |  |

|                     |                                              |           | high-20kV @10,000A                            | ,                                               |  |

#### Fuse Selection

Safety considerations may require a fuse in series with the mains connection. For an end product to continue to function (without user intervention) it is necessary that the selected fuse not open following a specified line surge. A minimum 6A time-lag ("slow blow") rating has been shown to be necessary to avoid unintentional fusing action at "high system exposure" levels of IEEE C62.41-1991.

If a coupling circuit which incorporates varistor protection is selected, the varistor manufacturer's recommendations for maximum fuse current should be followed. The vendor listed in the coupling circuits which follow suggests a maximum fuse rating of 6A for use with 7mm (1200A) varistors and a maximum rating of 18A for use with 14mm (4500A) varistors.

A 6A time-lag fuse is specified in all of the following coupling circuits since it satisfies all of the above criteria, as well as the critical requirement that it add very little resistance (<0.1 Ohms) to the transmit signal path. If a current rating greater than 6A is required by the application then either larger varistor (>7mm) or gas discharge tube protection is recommended.

# **Recommended Coupling Circuit Schematics**

This section provides schematics and component information for coupling the PLT-22 transceiver to the power mains. Three circuits are given, one each for isolated and non-isolated single phase coupling and one for 3-phase coupling. For each schematic, component specifications and suggested suppliers/part numbers are provided.

Vendor part number information is provided as a way to reduce component selection times, since the suggested parts have already been verified to meet all required specifications. Alternate component suppliers may be used provided that **all** specifications listed for each component are met.

# Example 1: A-Band, Line-to-Neutral (L-to-N), Non-Isolated Coupling Circuit

Figure 4.9 presents a schematic for a line-to-neutral, non-isolated mains coupling circuit. Table 4.3 lists component values and recommended suppliers/part numbers for coupling to the AC mains with a nominal line voltage in the range 100-240VAC.

Note: This optional circuit should be added to nodes where >20V impulse noise is expected at  $\geq$ 100Hz rate.

Figure 4.9 A-band, L-to-N, Non-Isolated Coupling Circuit Schematic

Table 4.3 A-band, 100-240VAC, L-to-N, Non-Isolated Coupling Circuit Component Values

| Comp    | Value                                | Specifications                                                                | Vendor / Part Number                    |

|---------|--------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------|

| C1      | 0.10µF                               | ±10%, •400VDC, metalized polyester <sup>(1)</sup>                             | Matsushita Electric / ECQ-E4104KF       |

| C2      | 0.82μF                               | ±5%, •50VDC, metalized polyester                                              | Matsushita Electric / ECQ-V1H824JL      |

| C3      | •120µF                               | ±20%, 16VDC, aluminum electrolytic,                                           | Matsushita Electric / ECA-1CFQ121       |

|         |                                      | • 0.3• ESR @100kHz                                                            |                                         |

| C4      | 4700PF                               | ±5%, •50VDC                                                                   | AVX / SR205A472JAA                      |

| C5      | 0.10µF                               | ±5%, •50VDC                                                                   | AVX / SR205C104JAA                      |

| D1      | 1A                                   | Reverse breakdown •50V, surge current •30A for 8.3mS, reverse recovery •200nS | 1N4935                                  |

| F1      | 6A                                   | 250VAC, slow blow <sup>(2)</sup>                                              |                                         |

| L1, L5  | 1.0mH                                | ±10%, Imax•30mA, R <sub>DC</sub> •50•                                         | TAIYO YUDEN / LAL03NA102K               |

| L3      | 1.5mH                                | ±10%, Imax•30mA, R <sub>DC</sub> •60•                                         | RCD/ALO5 1500µH KT                      |

| L2A     | 27μΗ                                 | ±10%, Imax •1A, R <sub>DC</sub> •0.1•                                         | TAIYO YUDEN /LHL08TB270K <sup>(6)</sup> |

| L2B     | 12µH                                 | ±10%, Imax •500mA, R <sub>DC</sub> •0.3•                                      | TAIYO YUDEN / LAL05TB120K               |